TECHNICAL MANUAL

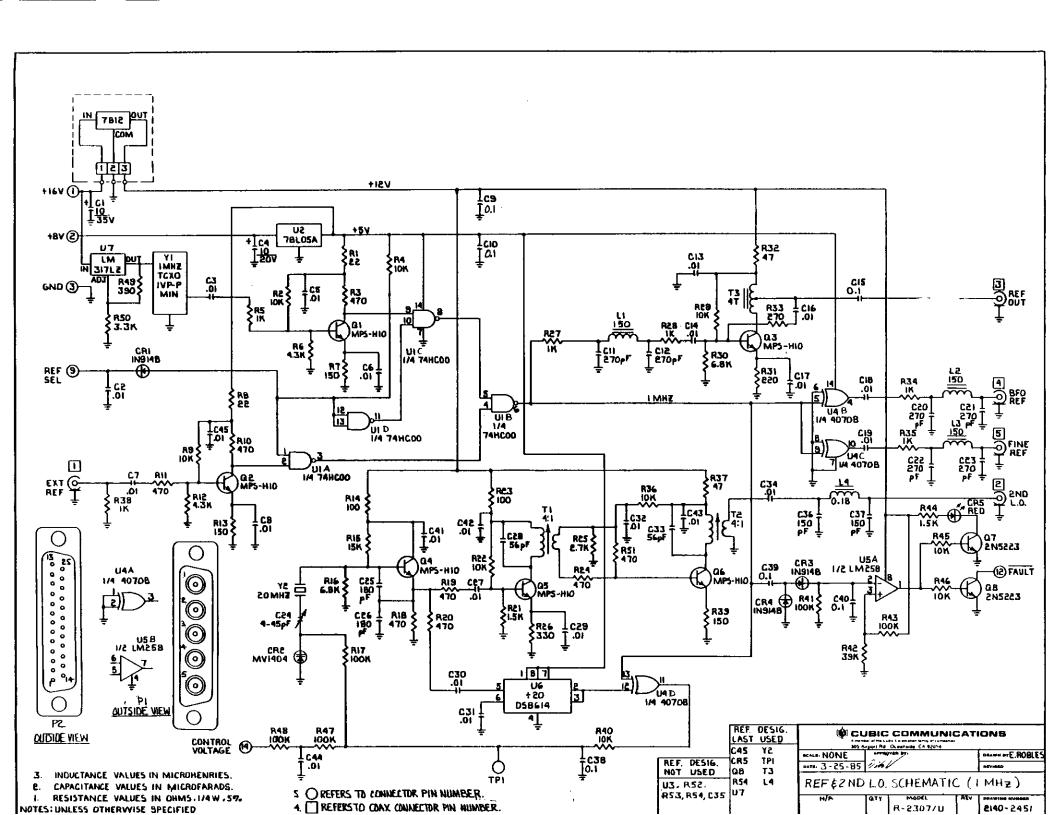

R-3930

RECEIVER, DUAL, VLF-HF

ond

R-3080

RECEIVER, HALF-RACK, SINGLE, VLF-HF

5 kHz to 30 MHz

ISSUE 3.0

FEBRUARY 1986

CUBIC COMMUNICATIONS, INC.

305 AIRPORT ROAD

OCEANSIDE, CALIFORNIA 92054

TELEPHONE: (619)-757-7525 TELEX: 695435 CUBICOM OCEN

## **SCOPE**

This manual has been prepared to help the equipment installer and operator get the best performance from either the R-3030 dual receiver or the R-3080 half-rack single receiver. It contains information about technical specifications, optional configurations, installation requirements, and operational procedures including operator maintenance and fault isolation to the module level.

Theory of operation and detailed circuit descriptions are included in an appendix to aid in the understanding of the operation of the equipment. This material is contained as an appendix due to the many variations in configuration resulting from customer requests and to accommodate improvements in design from the original configuration.

Maintenance, including component replacement and internal adjustments, will ordinarily be performed at the designated maintenance depot. Therefore, detailed fault isolation to the component level and repair information is not included in this manual. We urge that this manual be read from cover to cover before applying power to the equipment and that it be kept available for reference.

# WARNING NOTE

DO NOT APPLY POWER TO THIS EQUIPMENT UNTIL THIS MANUAL IS READ AND UNDERSTOOD.

## PROPRIETARY DATA

The information contained in this document is the property of Cubic Communications, Vo on a party, eliner wholly of in part, without the worth consent of Communications, Inc.

Cubic Communications granted AMRAD the right to distrubute freely to Radio Amateurs

## CORRECTION NOTICE

The information contained in this document is believed to be correct as of the date of publication. Any errors noted within are requested to be directed to the factory for correction of future issues and update of existing issues.

# RIGHTS RESERVED

Cubic Communications, Inc. reserves the right to change the specifications, design details, and method of fabrication of these receivers at any time without notice. If a variation is noted between the contents of this manual and the equipment in your possession, contact the factory for clarification and/or additional documentation.

#### STANDARD COMMERCIAL WARRANTY

Cubic Communications, Inc. warrants their equipment to be free from defects in material and workmanship, except for tubes and solid-state devices, under normal use and service when used for the purpose for which designed, for a period of one year from date of shipment, provided that the notice of such defect is given to Cubic Communications, Inc., or its authorized service depot, within 60 days after discovery thereof and provided that inspection by Cubic Communications, Inc., or its authorized service depot, indicates the equipment or parts are defective to Cubic Communications, Inc. reasonable satisfaction. Tubes and solid-state devices are warranted for a period of ninety days.

Cubic Communications, Inc.'s obligations under this warranty are limited to the repair or replacement of defective parts and the return of such repaired or replaced parts to the purchaser. At Cubic Communications, Inc.'s option, any defective part shall be returned to the factory for inspection, properly packed and all expenses prepaid. No equipment or parts shall be returned unless the purchaser first obtains prior approval from Cubic Communications, Inc. Equipment furnished by, but manufactured by another, bears only the warranty given by such other manufacturer, which will be furnished on request.

No warranties other than those expressly stated herein are given or implied with respect to the equipment furnished and Cubic Communications, Inc. shall in no event be liable for consequential damages, or for loss, damage, or expense directly or indirectly arising from the use of the products, or any inability to use them either separately or in combination with other equipment or materials, or from any other cause.

- 242 6

ا بالمنافق الله المنافق المنافق

## TABLE OF CONTENTS

| 1.0                                                                         | INTRODUCTION1-1                                                                                                                                                                                       |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0                                                                         | SPECIFICATIONS2-1                                                                                                                                                                                     |

| 2.1                                                                         | PERFORMANCE2-1                                                                                                                                                                                        |

|                                                                             | 2.1.1       Frequency                                                                                                                                                                                 |

| 2.2                                                                         | ENVIRONMENTAL                                                                                                                                                                                         |

| 2.3                                                                         | PHYSICAL       2-13         2.3.1 Construction       2-13         2.3.2 Maintainability       2-13         2.3.3 Size       2-13         2.3.4 Weight       2-13         2.3.5 Reliability       2-13 |

| 3.0                                                                         | INSTALLATION3-1                                                                                                                                                                                       |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11 | UNPACKING AND INSPECTION                                                                                                                                                                              |

## TABLE OF CONTENTS (continued)

| 4.0               | OPERAT!ON4-                          | 1           |

|-------------------|--------------------------------------|-------------|

| 4.1               | MANUAL OPERATION4-                   | 2           |

|                   | 4.1.1 NORMAL STATE                   | 4<br>5<br>7 |

| 4.2               | REMOTE OPERATION VIA TEEE-488 BUS4-1 | 0           |

|                   | 4.2.1 IEEE-488 BUS DESCRIPTION       | 1<br>3      |

| 4.3               | REMOTE OPERATION VIA SERIAL BUS4-1   | 4           |

|                   | 4.3.1 TRANSMISSION FORMAT            | 6<br>7      |

| 5.0               | OPERATIONAL MAINTENANCE5-            | 1           |

| 5.1<br>5.2<br>5.3 | FAULT ISOLATION                      | 5           |

| 6.0               | THEORY OF OPERATION6-                | 1           |

| 6.1<br>6.2<br>6.3 | RECEIVER SECTION                     | 5           |

| 7.0               | REPLACEABLE MODULES7-                | 1           |

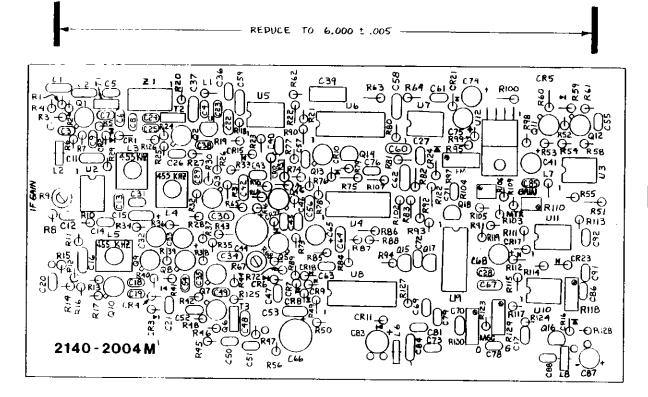

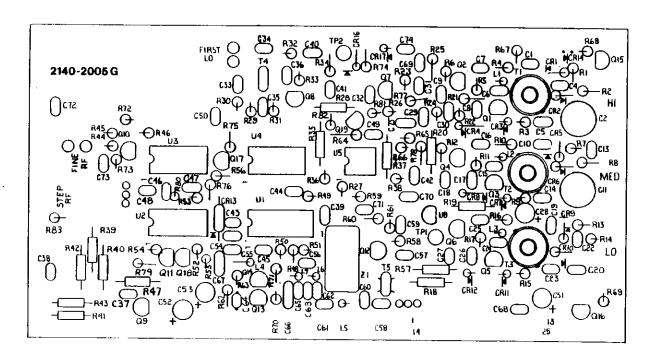

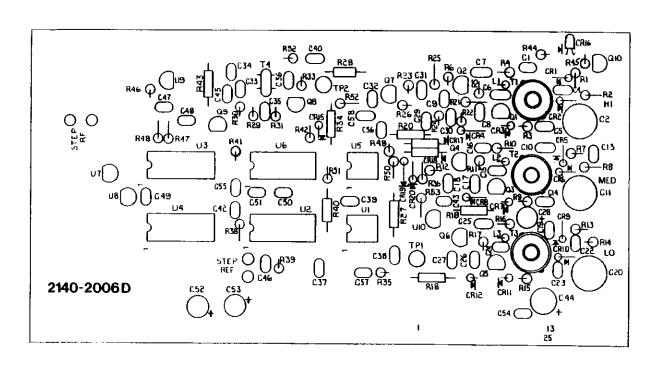

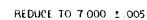

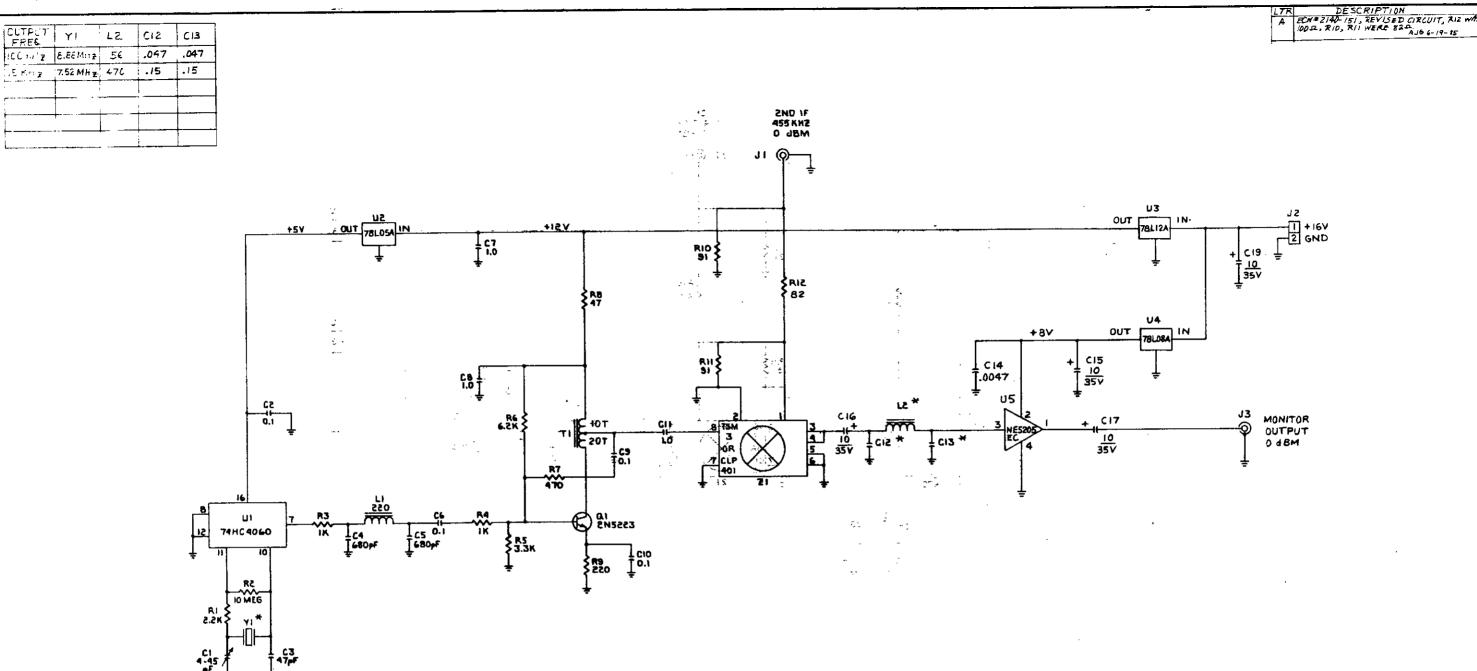

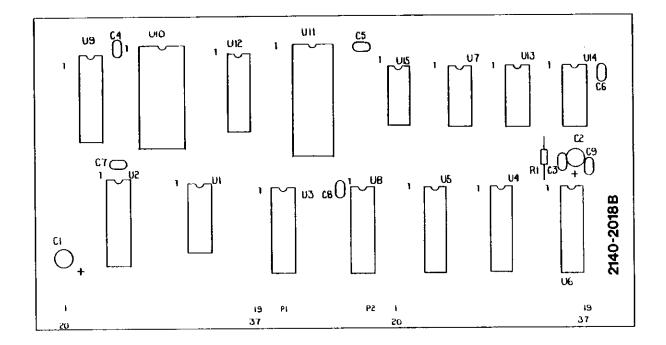

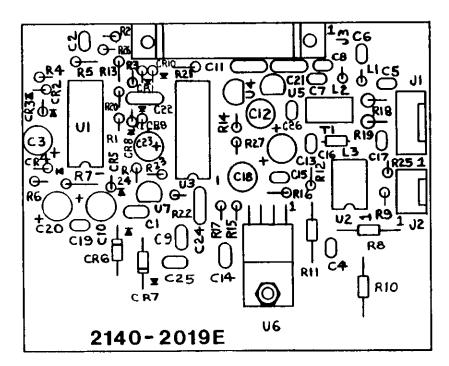

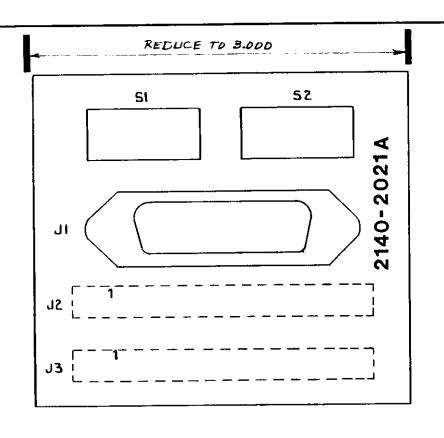

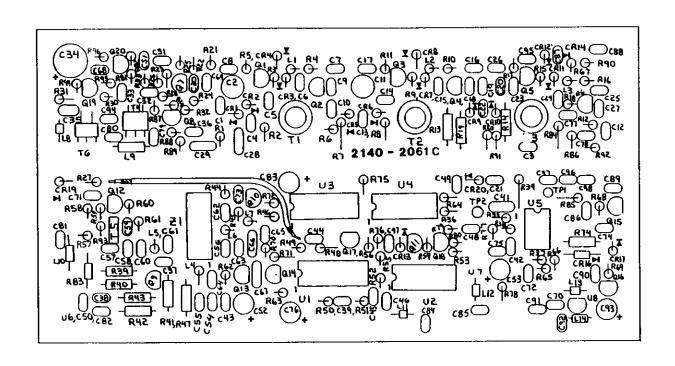

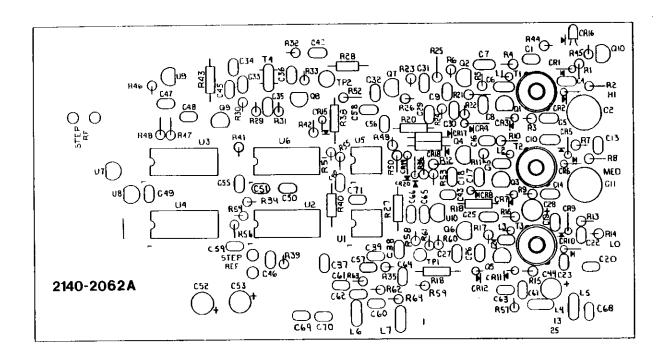

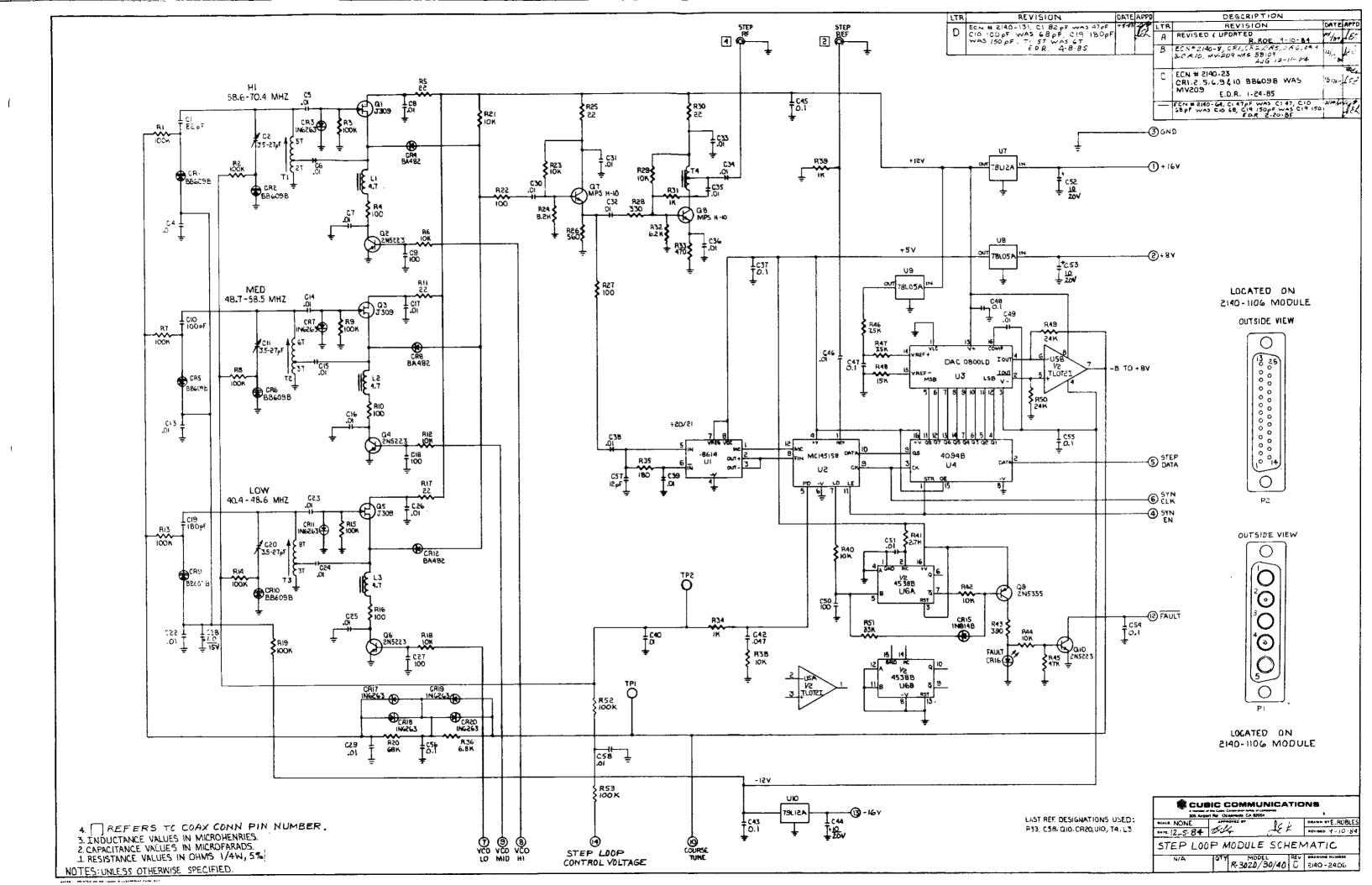

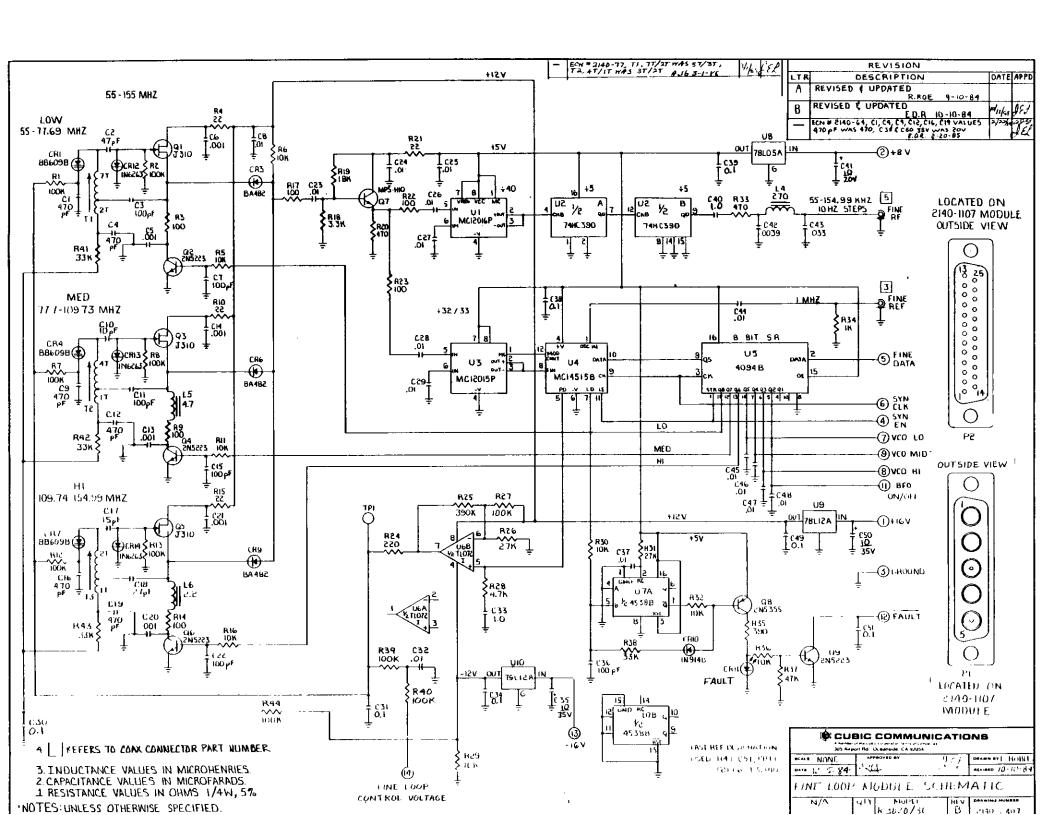

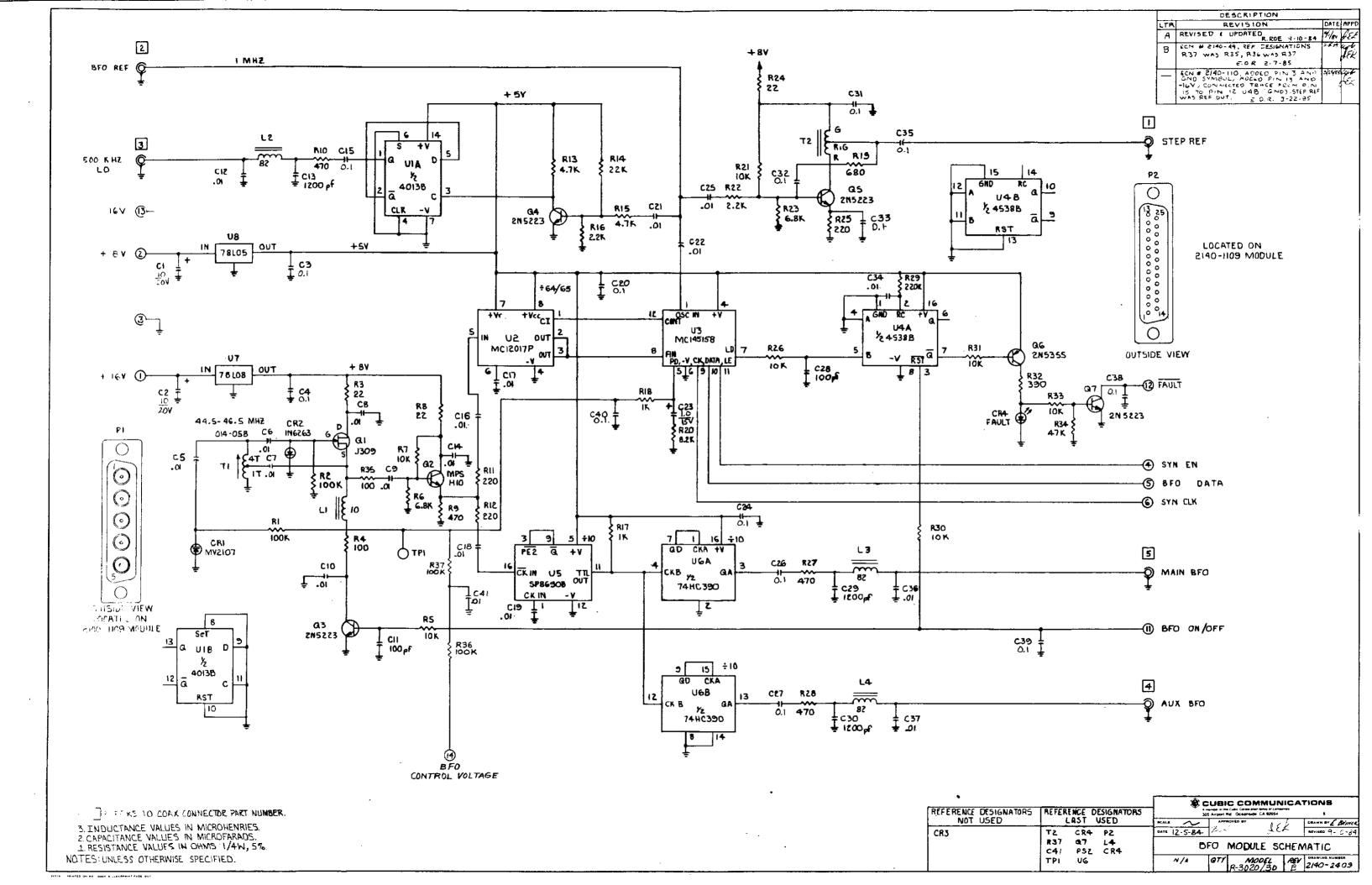

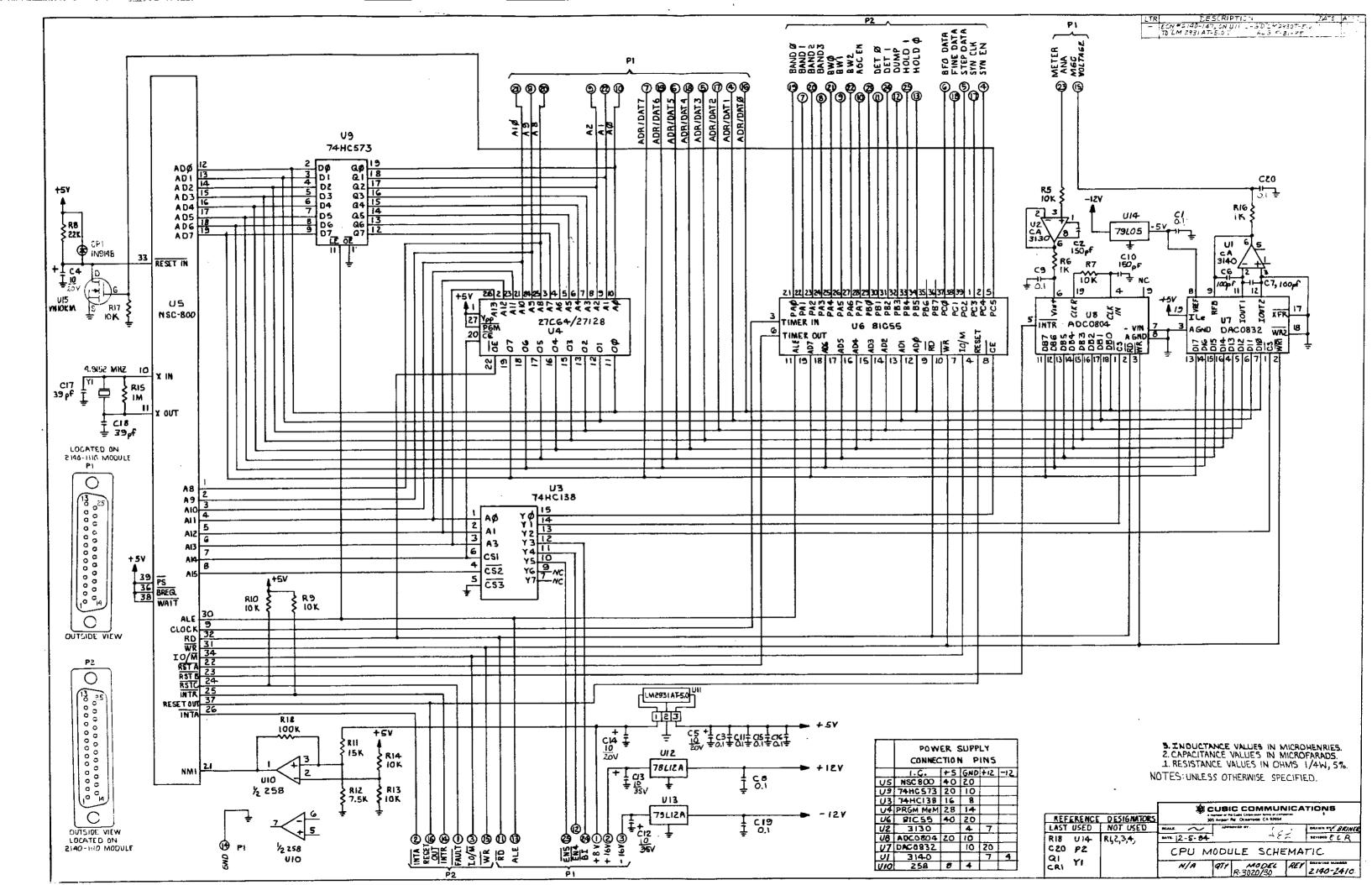

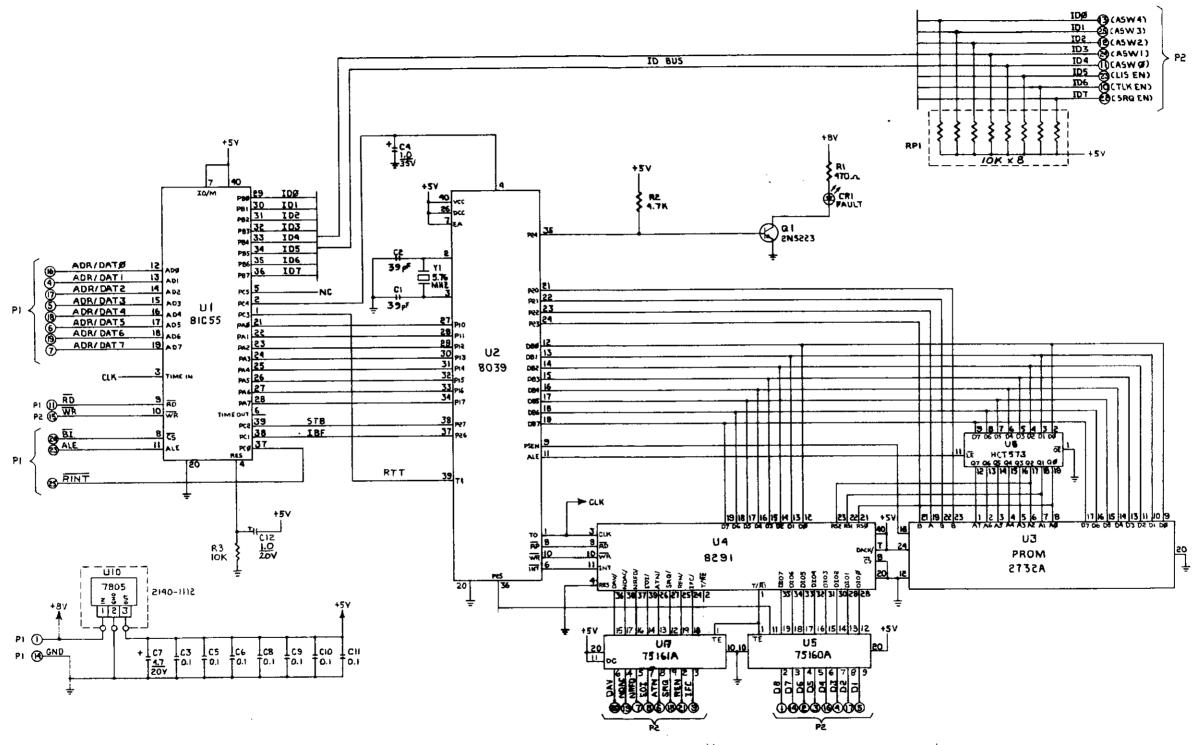

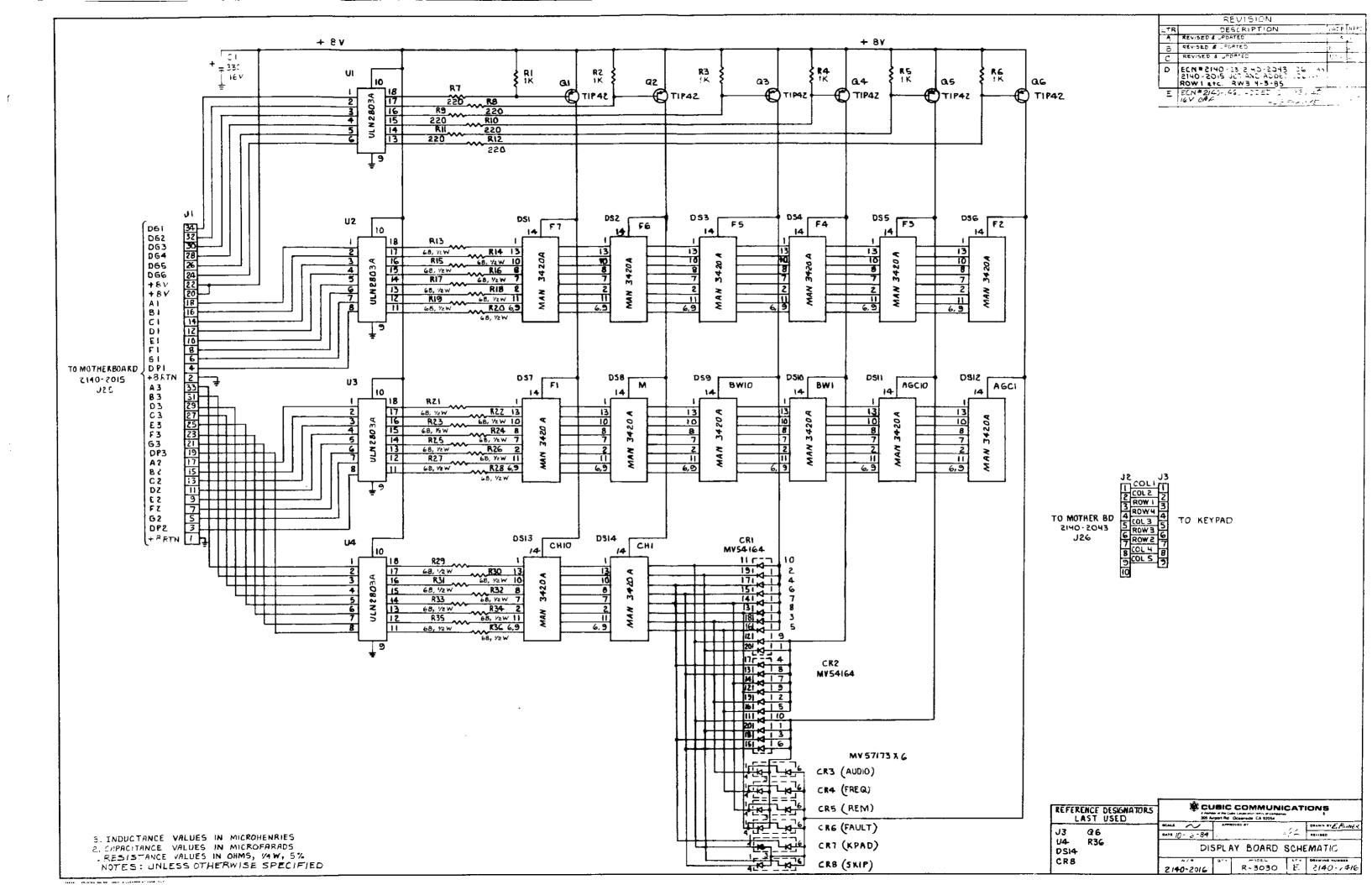

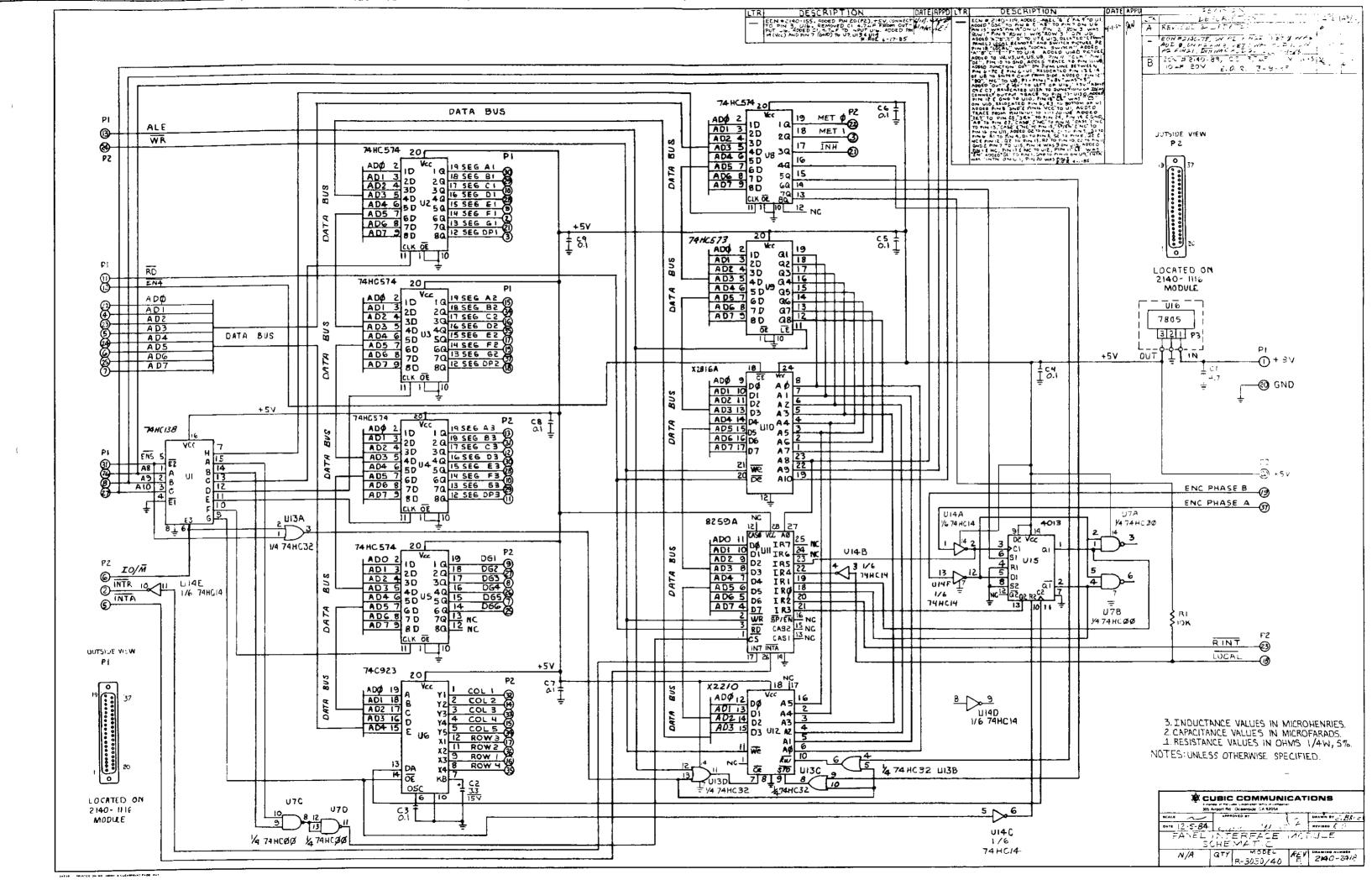

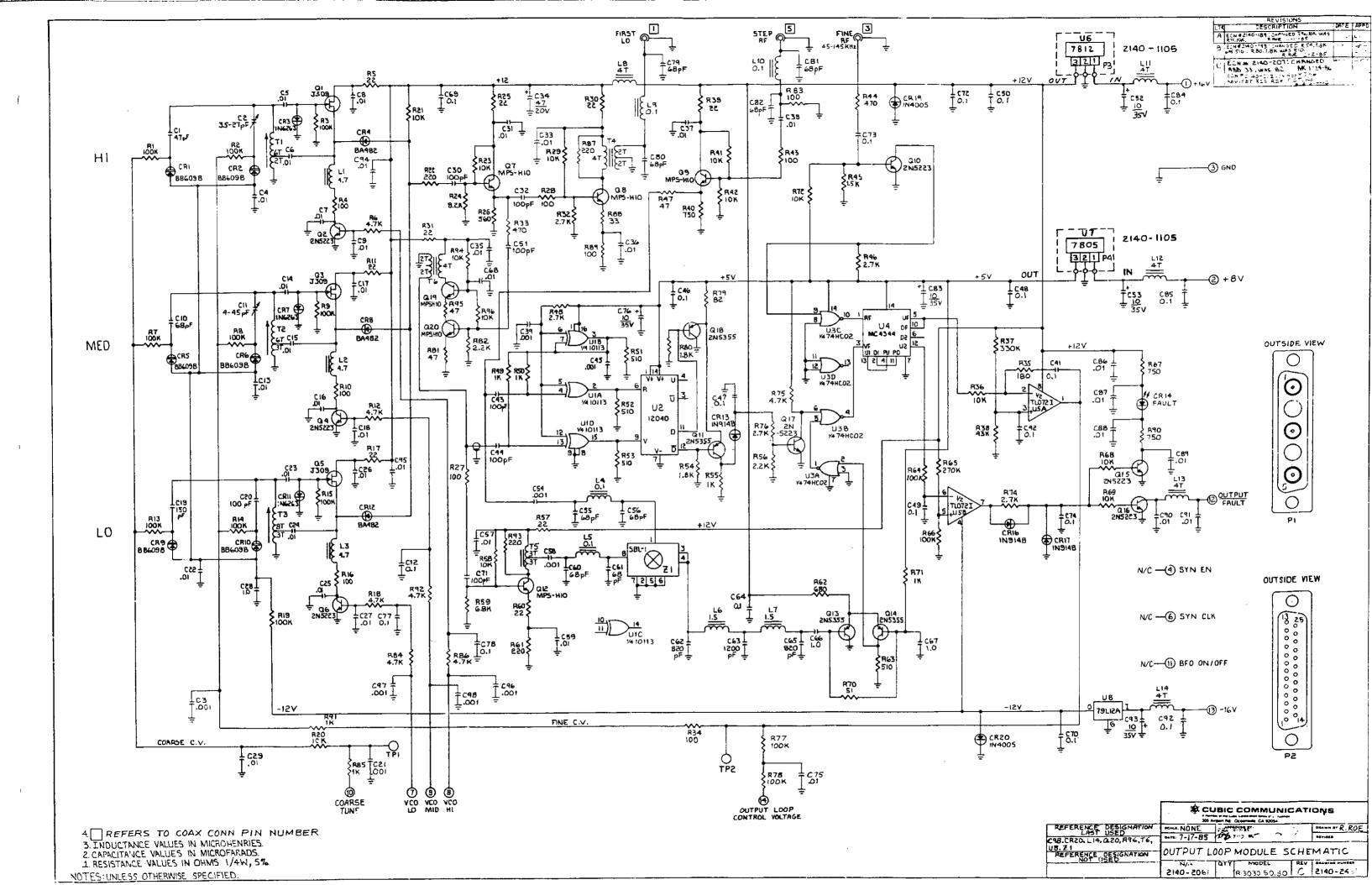

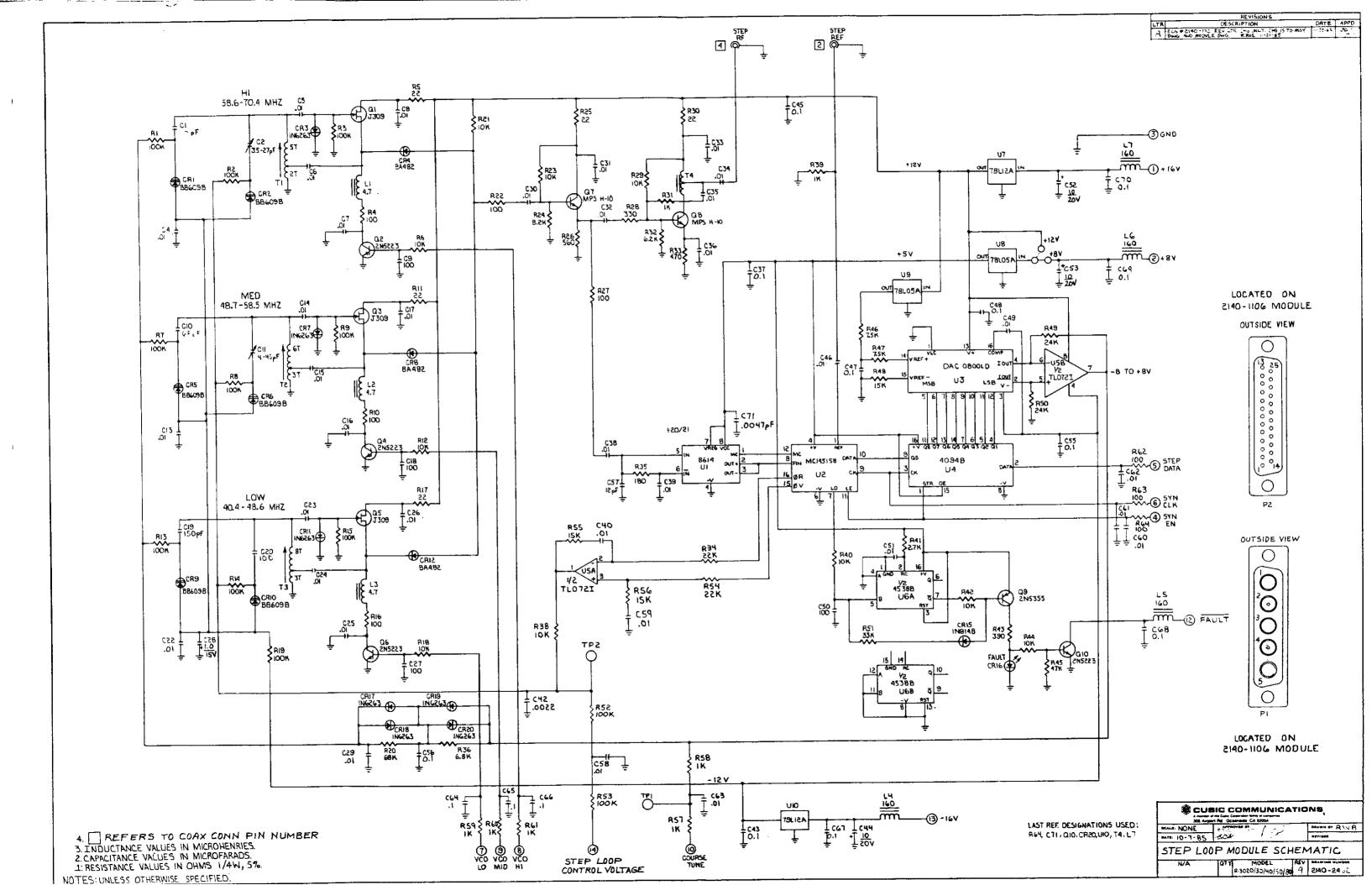

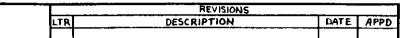

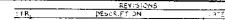

APPENDIX -- MODULE DESCRIPTIONS AND DIAGRAMS

## LIST OF ILLUSTRATIONS

| FIGURE           | DESCRIPTION                                                | PAGE |

|------------------|------------------------------------------------------------|------|

| 1-1              | R-3030 PHOTOGRAPH                                          | 1-2  |

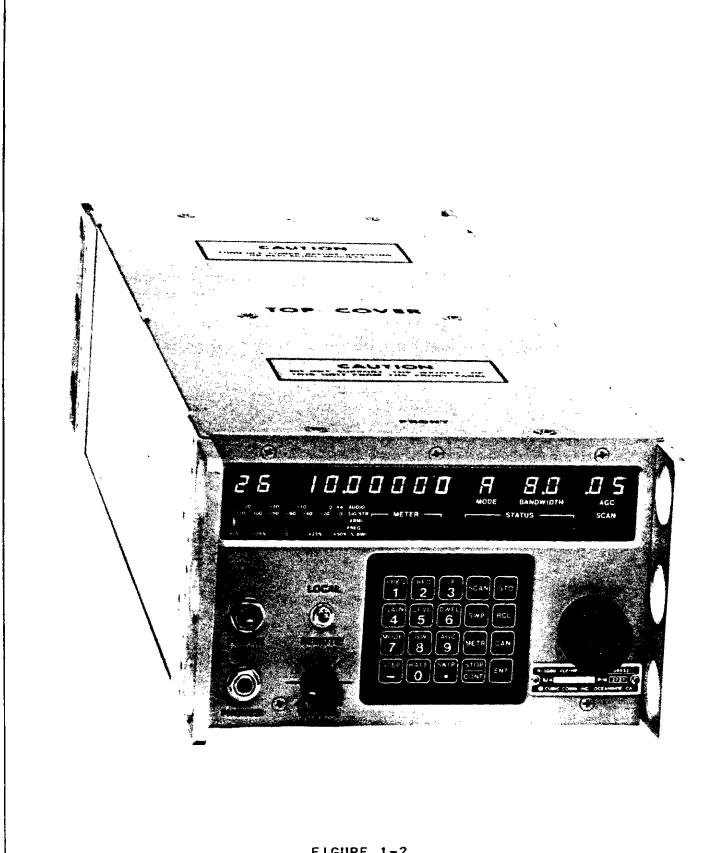

| 1-2              | R-3080 PHOTOGRAPH                                          | 1-3  |

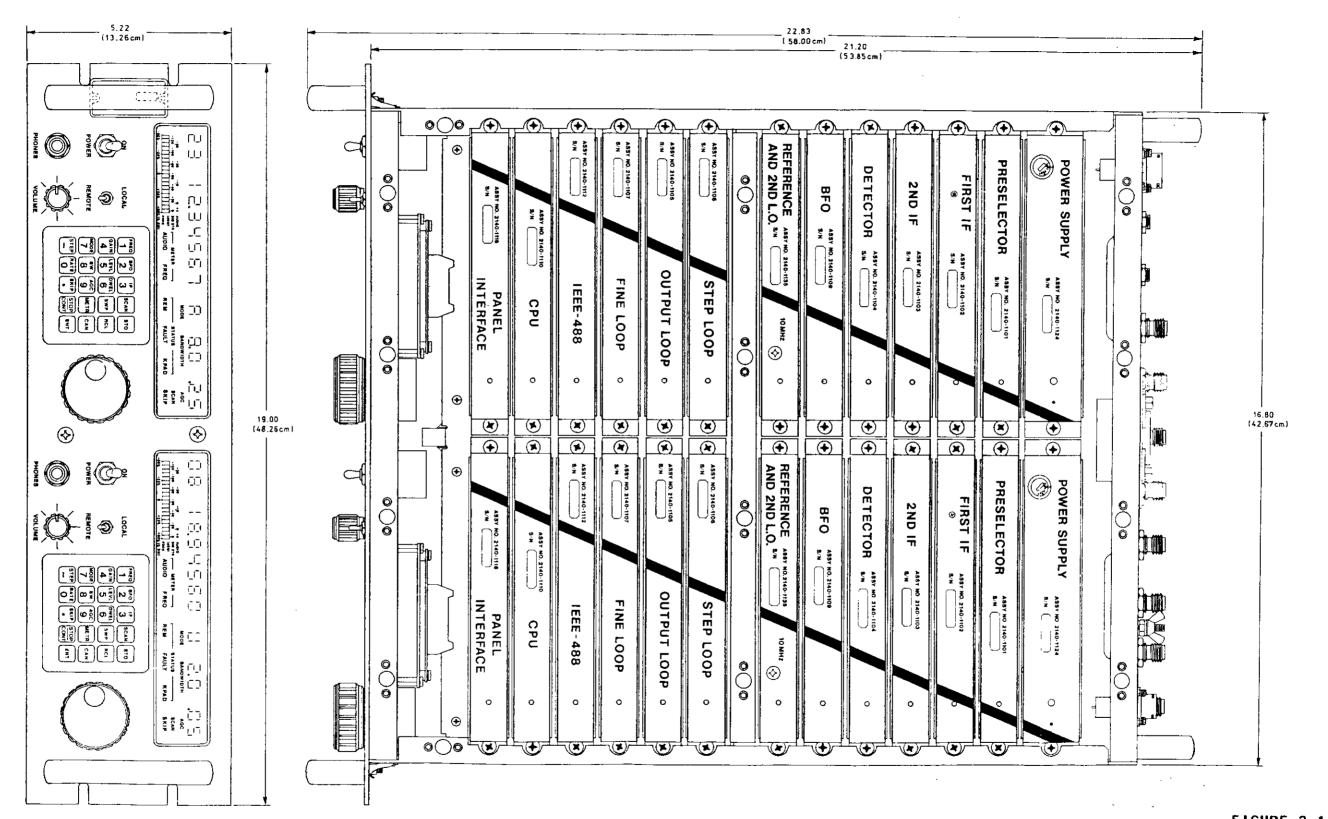

| 2-1              | R-3030 OUTLINE AND MOUNTING DRAWING                        | 2-15 |

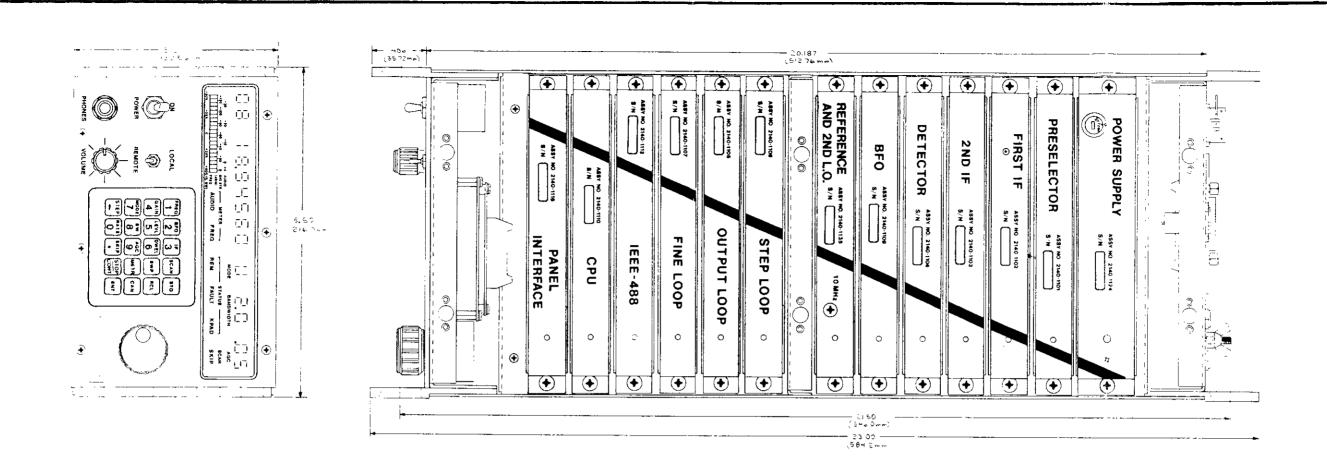

| 2-2              | R-3080 OUTLINE AND MOUNTING DRAWING                        |      |

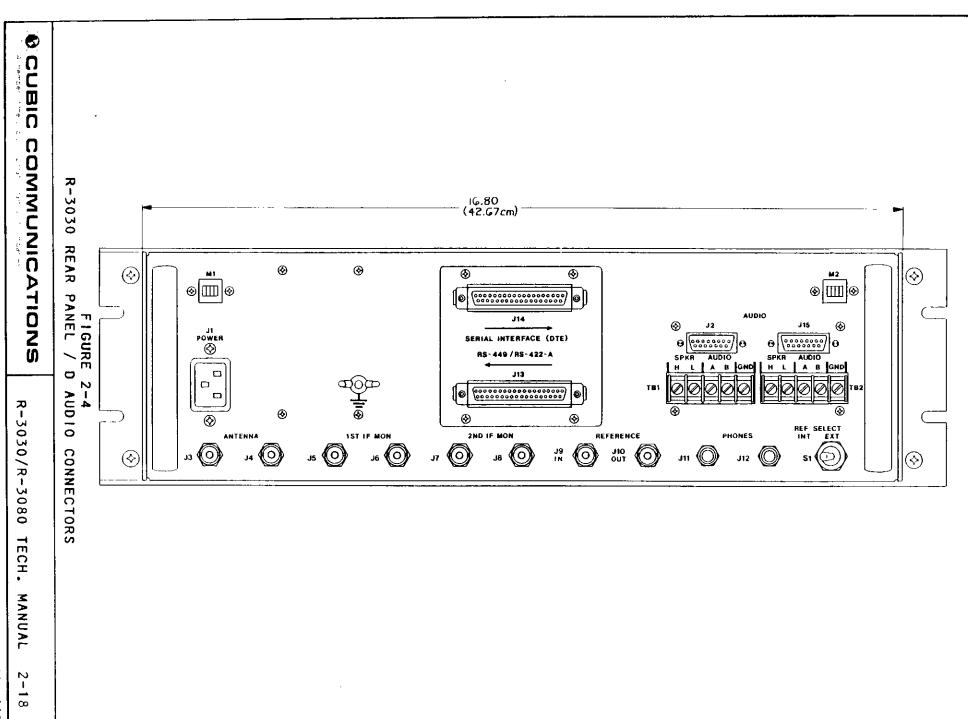

| 2 <b>-</b> 3     | R-3030 REAR PANEL / MS AUDIO CONNECTOR                     | 2-17 |

| 2-4              | R-3030 REAR PANEL / D AUDIO CONNECTORS                     |      |

| 2 <b>-</b> 5     | R-3080 REAR PANEL / MS AUDIO CONNECTOR                     |      |

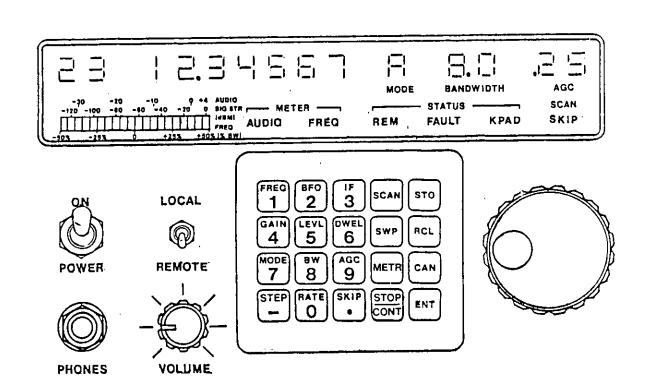

| 4-1              | CONTROL PANEL PICTORIAL                                    |      |

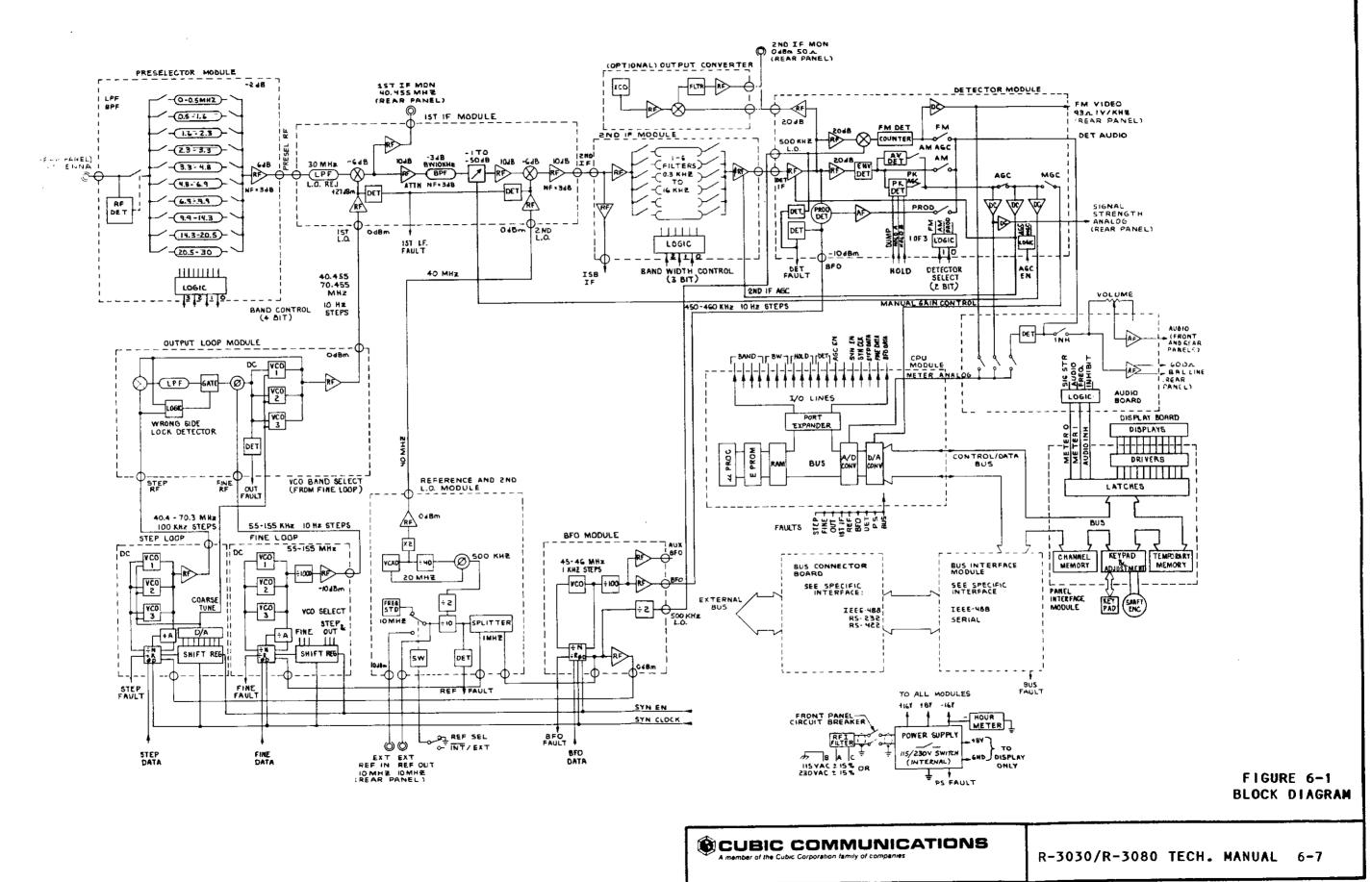

| 6-1              | RECEIVER BLOCK DIAGRAM                                     | 6-7  |

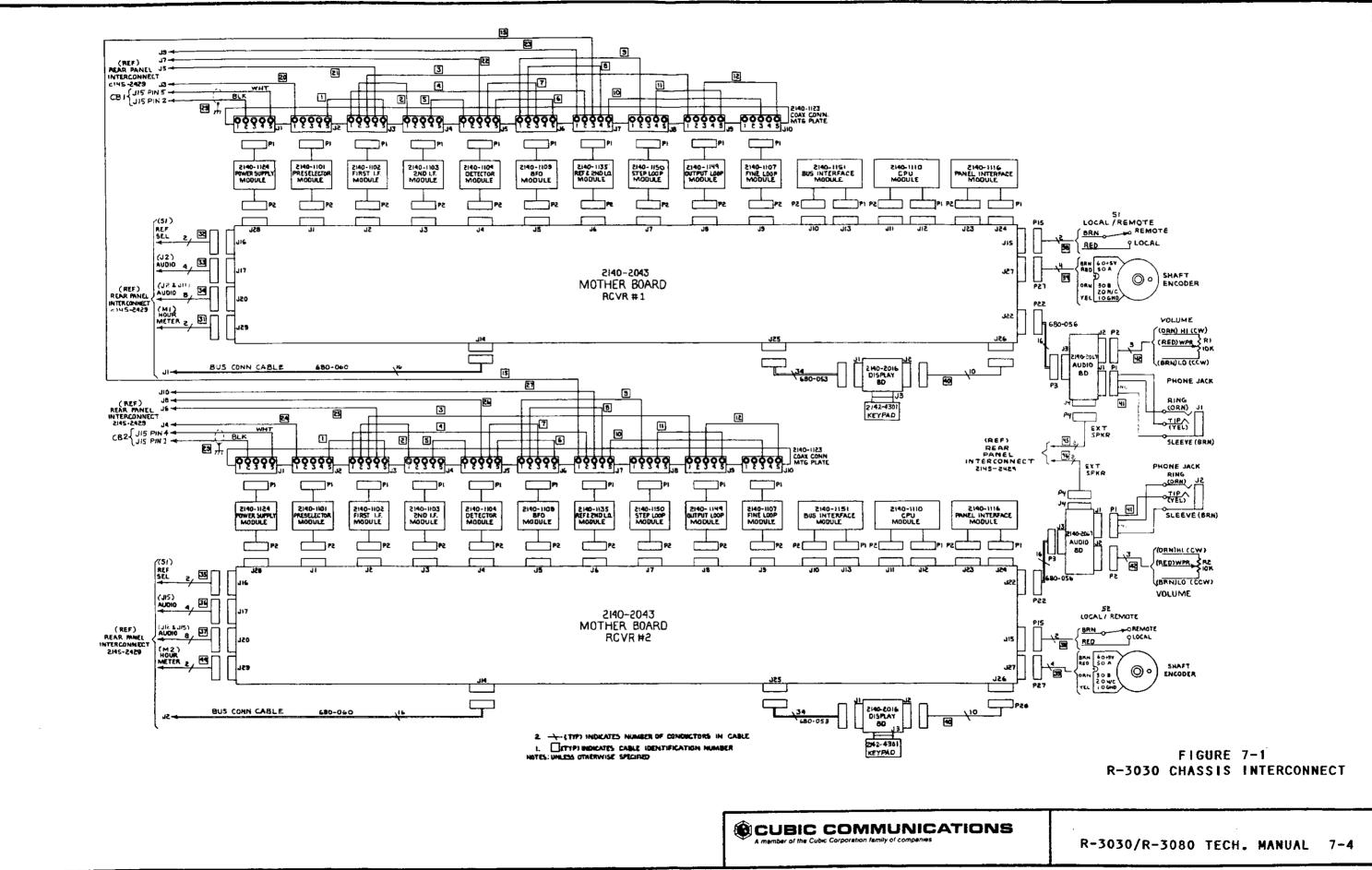

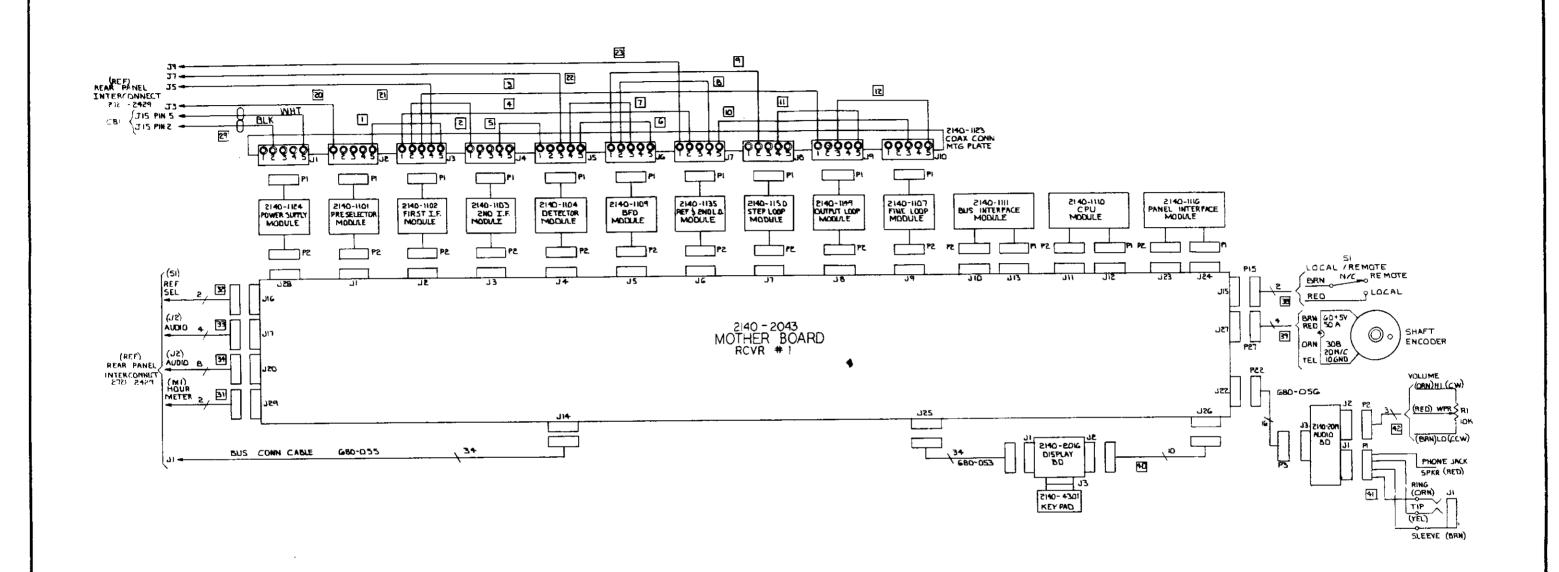

| 7-1              | R-3030 CHASSIS INTERCONNECT DIAGRAM                        |      |

| 7 <del>-</del> 2 | R-3080 CHASSIS INTERCONNECT DIAGRAM                        |      |

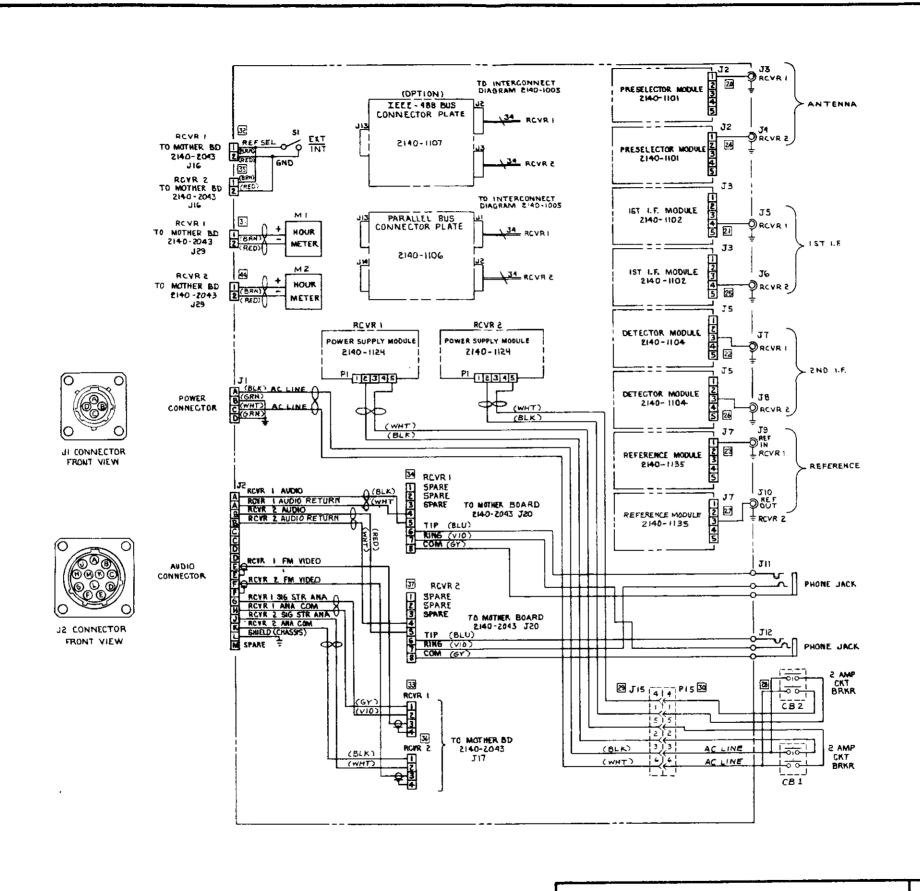

| 7-3              | R-3030 REAR PANEL INTERCONNECT / 12 PIN MS AUDIO CONNECTOR | 7-6  |

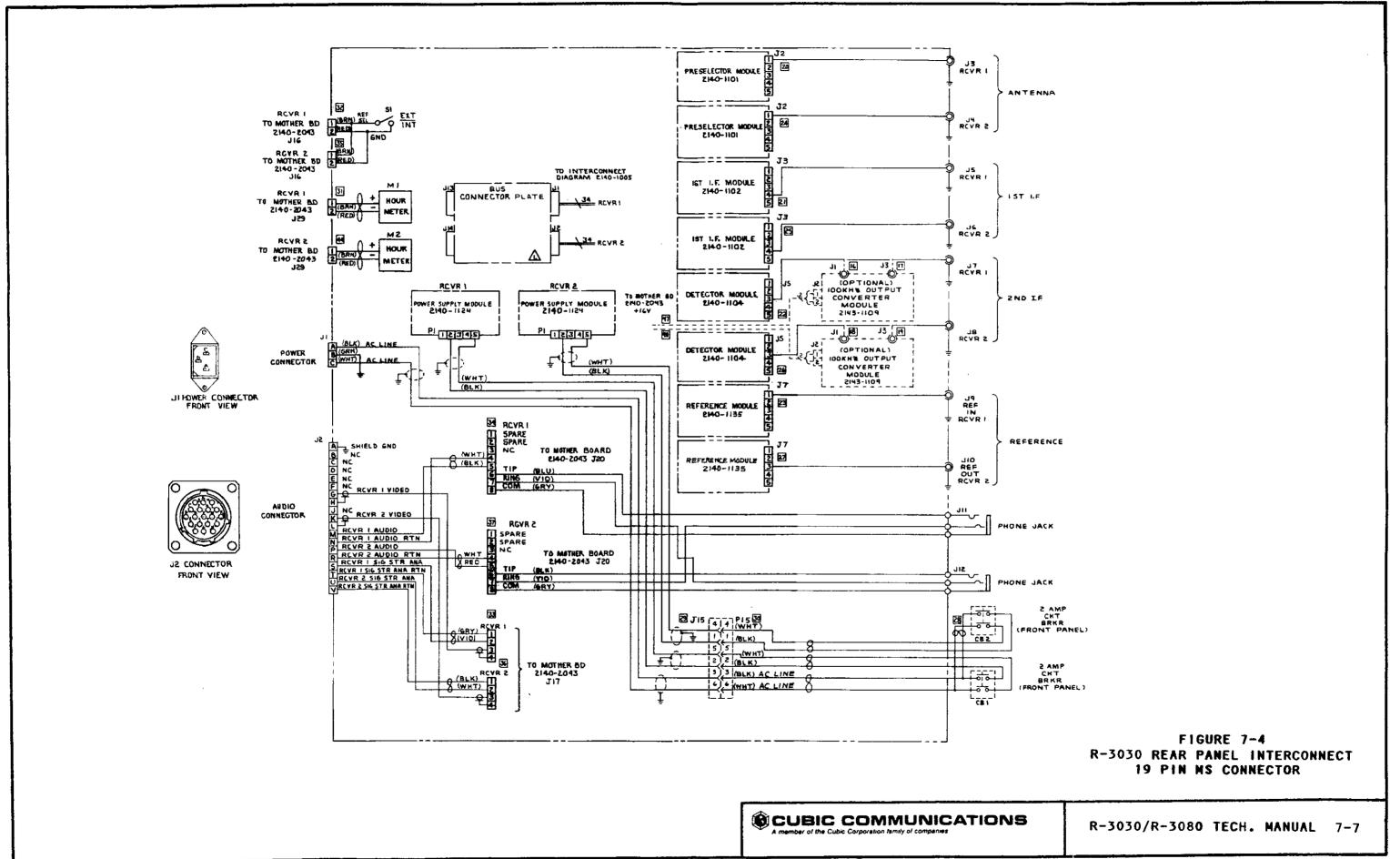

| 7-4              | R-3030 REAR PANEL INTERCONNECT / 19 PIN MS AUDIO CONNECTOR | 7-7  |

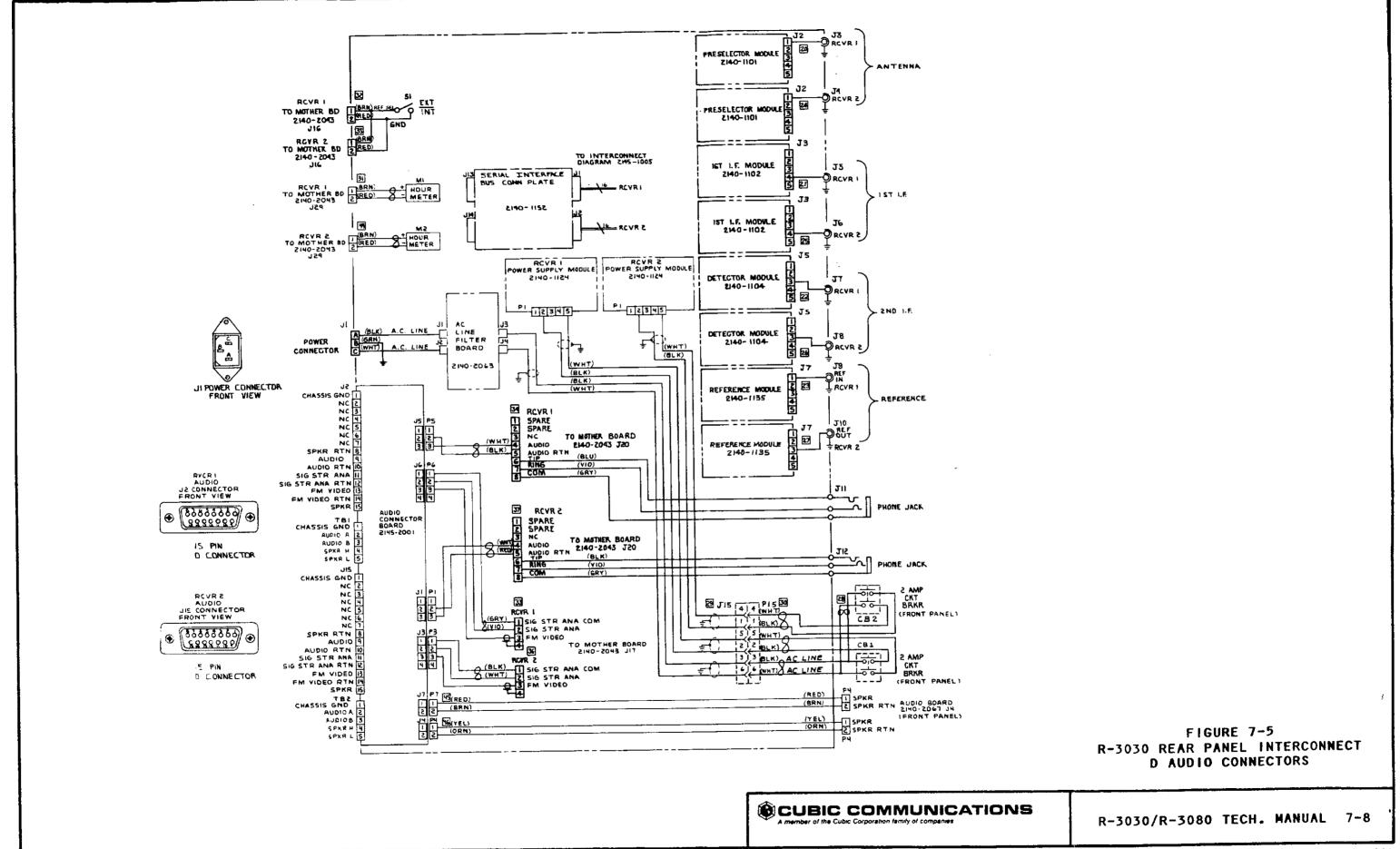

| 7 <del>-</del> 5 | R-3030 REAR PANEL INTERCONNECT / D AUDIO CONNECTORS        | 7-8  |

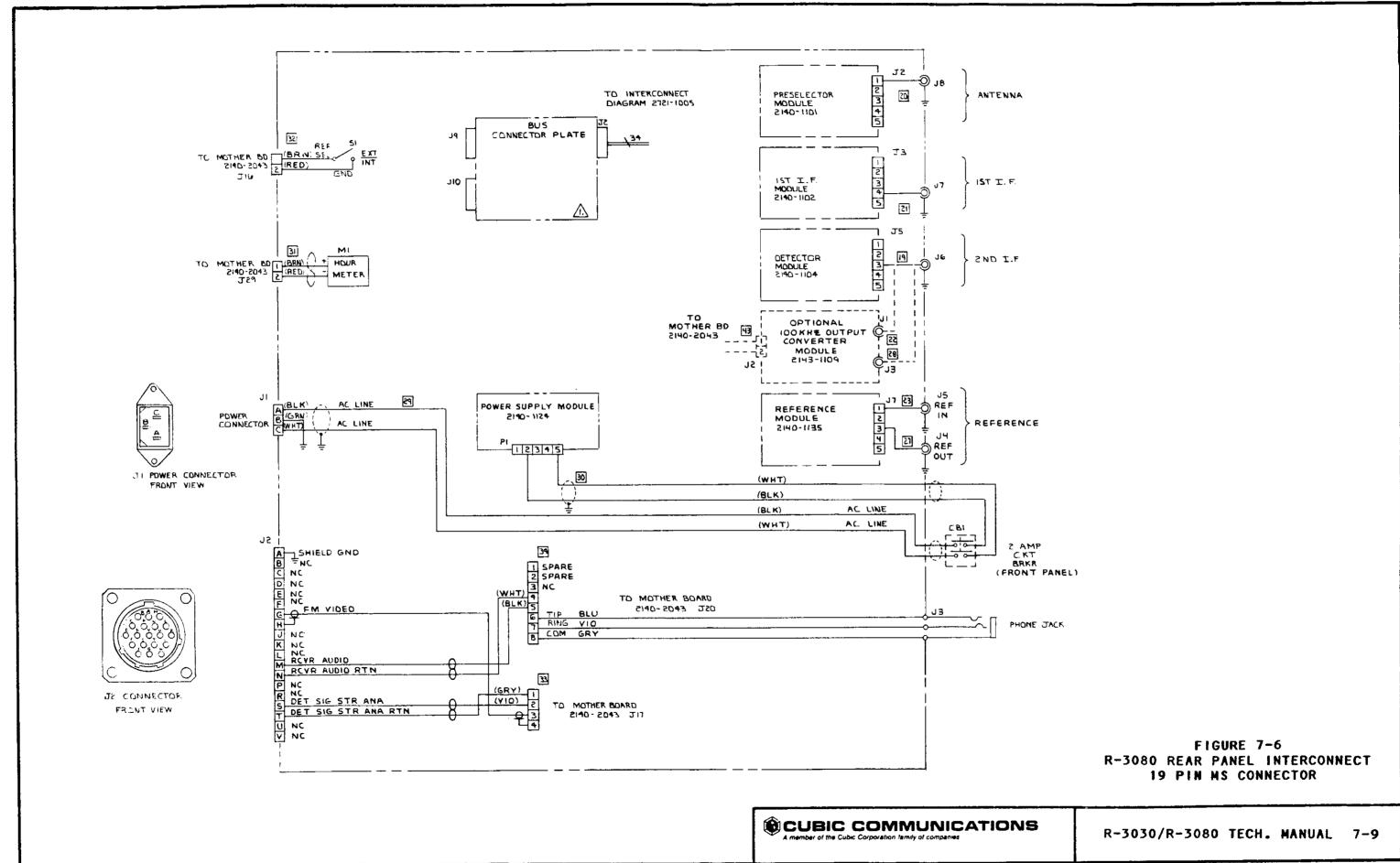

| 7-6              | R-3080 REAR PANEL INTERCONNECT / 19 PIN MS AUDIO CONNECTOR | 7-9  |

#### 1.0 INTRODUCTION

The R-3030 and R-3080 are high performance multi-mode receivers tuning the frequency range from 5 kHz to 30 MHz and having usable performance from 50 KHz to 30 MHz. The intended use of this receiver is in manually operated or remote controlled arrays of receivers. The R-3030 in its various configurations contains two receivers in one chassis while the R-3080 is a single receiver in a chassis half the width of a standard rack chassis. Each receiver may be assigned a unique address and can be operated in groups of up to 14 receivers via an IEEE-488 remote control bus or in groups of up to 99 receivers via a serial control bus. A complete set of front panel controls and displays is also provided.

The type of remote control bus, selection of bandpass filter bandwidths, and external reference frequency (10 or 1 MHz) are option items selected at the time of order. These items may be changed in the field if required. Contact the factory for details. Filter and bus changes require software changes.

Receivers are comprised of individually shielded module assemblies. Each receiver has individual RF input and IF output connections and individual power supplies with individual power switches. One external frequency standard input connector and one frequency standard output connector with a single internal/external frequency standard selector switch is provided for each single or dual receiver assembly.

Manual operation of this receiver is by means of a 20 button keypad used for selection of frequency, mode, BFO and IF shift, manual gain, and other parameters. A manual adjustment knob is also provided for control of many of the above parameters. The display for this receiver includes frequency, mode, bandwidth, and AGC time constant as well as (when selected), BFO and IF shift, manual gain, threshold for squelch or scan stop, and other parameters. Each unit also contains a light bar type meter for indication of signal strength, audio signal level, or relative frequency of the input signal.

Operation of this receiver may also be entirely under the control of the computer system operator via the remote control bus. Choice of tuned frequency, mode, BFO offset (when the CW mode is selected), AGC time constant, and other parameters is all performed through the system console.

By proper selection of mode, bandwidth, BFO offset, gain control, AGC time constants, and other parameters, the operator is able to detect and demodulate a wide variety of signals including amplitude modulated, on/off keyed, and single sideband signals including full carrier, reduced carrier, and suppressed carrier signals. Frequency shift keyed signals can be demodulated as single sideband suppressed carrier signals or as true FM signals. All detector outputs are available as fixed level audio signals on a 600 ohm balanced line and the FM detector output is also available as a DC coupled signal on a single ended line. Headphone jacks are provided on both front and rear panels — the signal level on these headphone jacks is controlled by a front panel volume control.

First IF output signals at 40.455 MHz and second IF output signals at 455 KHz are brought out for display or analysis by other equipment. On special order, the normal 455 kHz output may be converted to another frequency.

© CUBIC COMMUNICATIONS

R-3030/R-3080 TECH. MANUAL

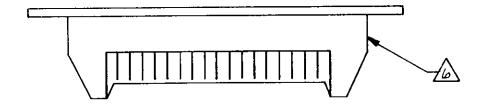

FIGURE 1-2 R-3080 PHOTOGRAPH

© CUBIC COMMUNICATIONS

R-3030/R-3080 TECH. MANUAL 1-3

| - |  |  |  |  |

|---|--|--|--|--|

|   |  |  |  |  |

#### 2.0 SPECIFICATIONS

#### 2.1 PERFORMANCE

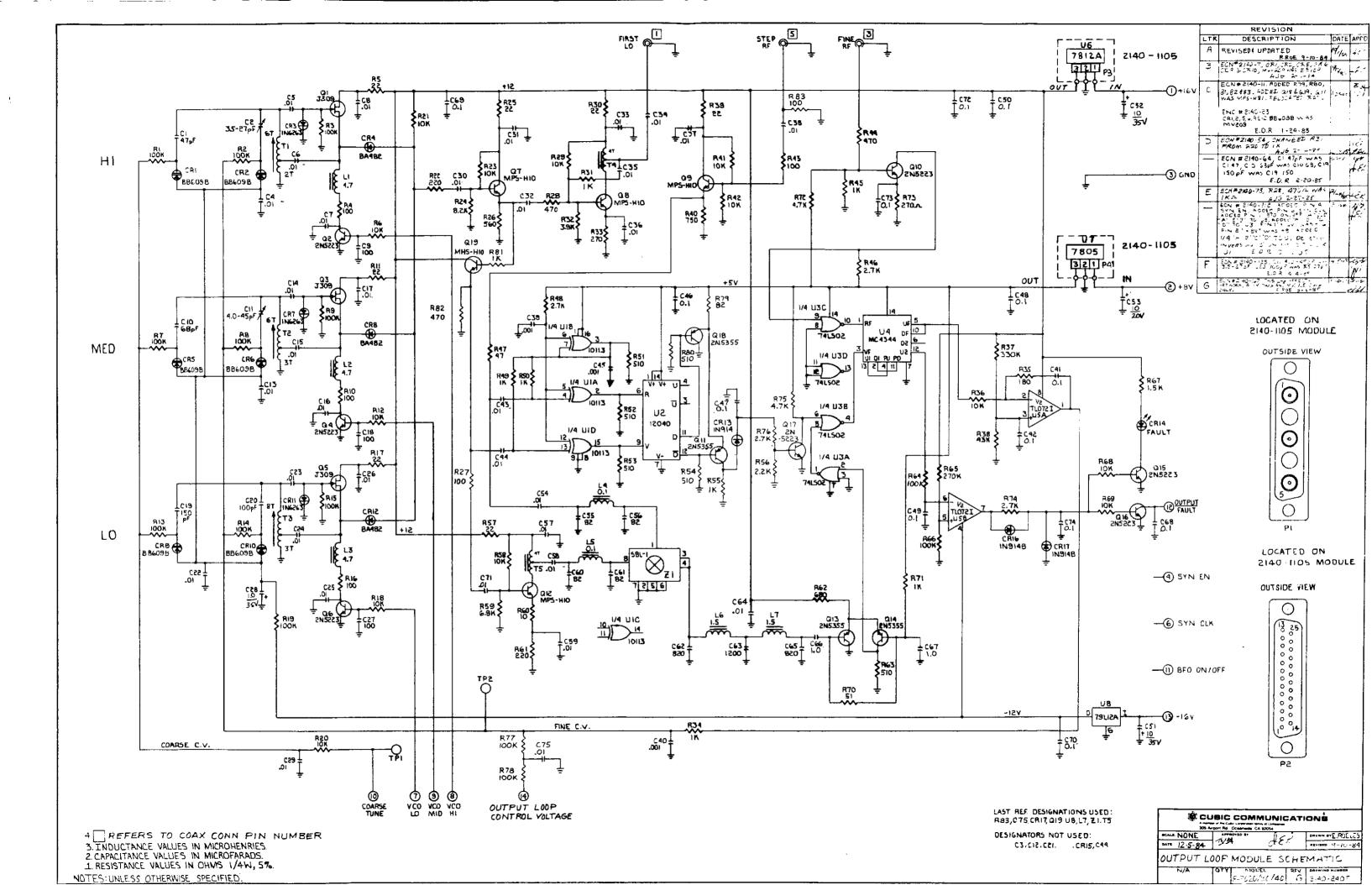

#### 2.1.1 Frequency

Range 5 kHz - 30 MHz (Tunes to 0 Hz, optimum above 50 kHz)

Resolution 10 Hz steps

Accuracy 1 part per million over temperature range

.01 parts per million per week aging

External Standard Input/Output: 1 or 10 MHz (Option), 0 dBm, 50 ohms

Synthesizer Lock Time 5 ms typical, 15 ms worst case

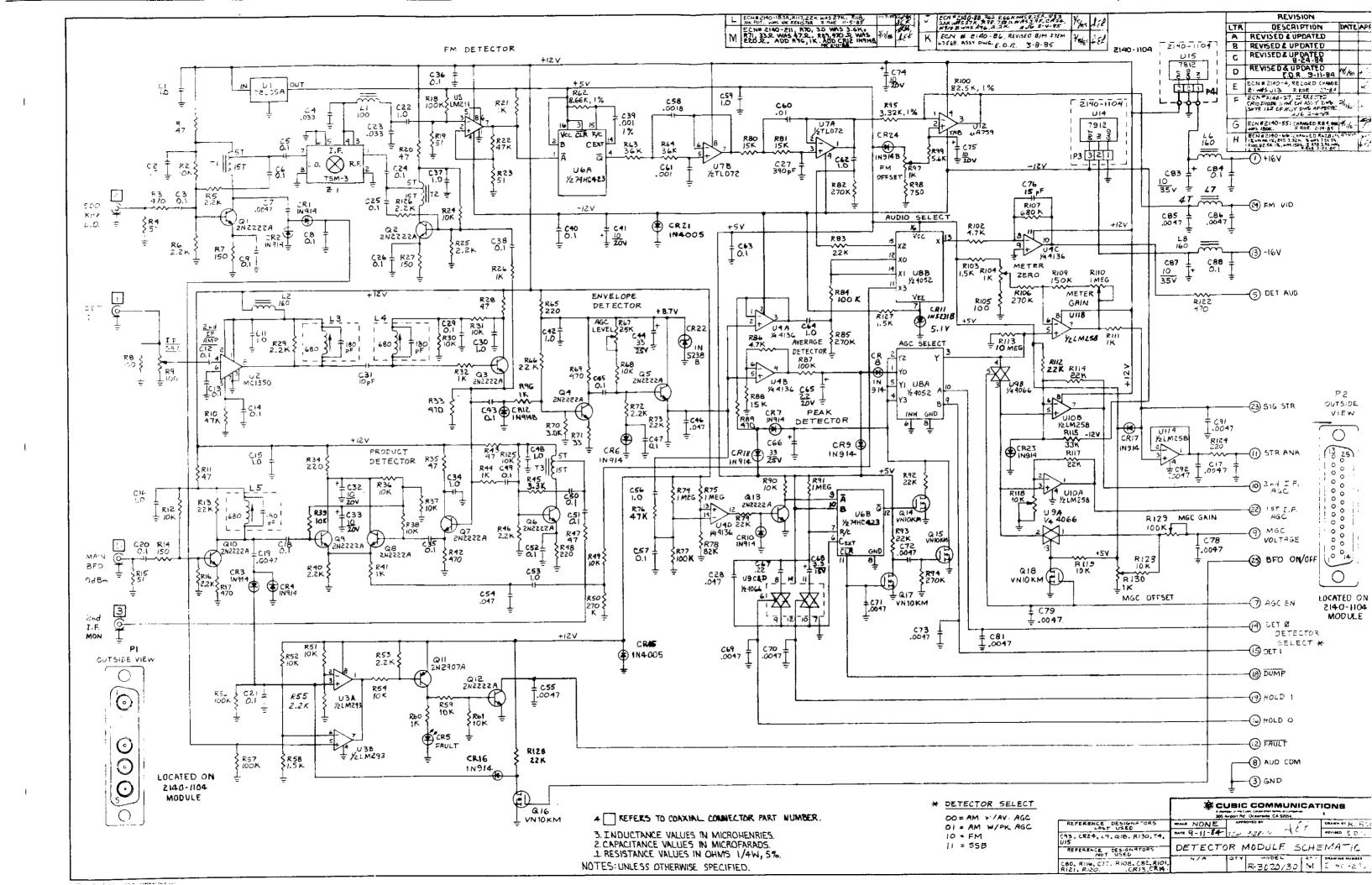

2.1.2 Modes

Selectable LSB, USB, AM, CW, FM

Always Active FM Video

#### 2.1.3 RF Section

| Inpu†<br>Inpu† VSWR | 50 ohms, TNC or BNC female (Option)<br>less than 3:1                                        |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| Protection          | Withstands application of RF power up to 100 Volts RMS from a 50 ohm source without damage. |  |  |  |  |  |

| Noise Figure        | 13 dB maximum above 1600 kHz, slight degradation below                                      |  |  |  |  |  |

| Sensitivity for     | SSB (2 kHz Bandwidth) -118 dBm                                                              |  |  |  |  |  |

Sensitivity for SSB (2 kHz Bandwidth) -118 dBm

10 dB SINAD CW (500 Hz Bandwidth) -124 dBm

(above 1600 kHz) AM (8 kHz Bandwidth, 90% modulation) -110 dBm

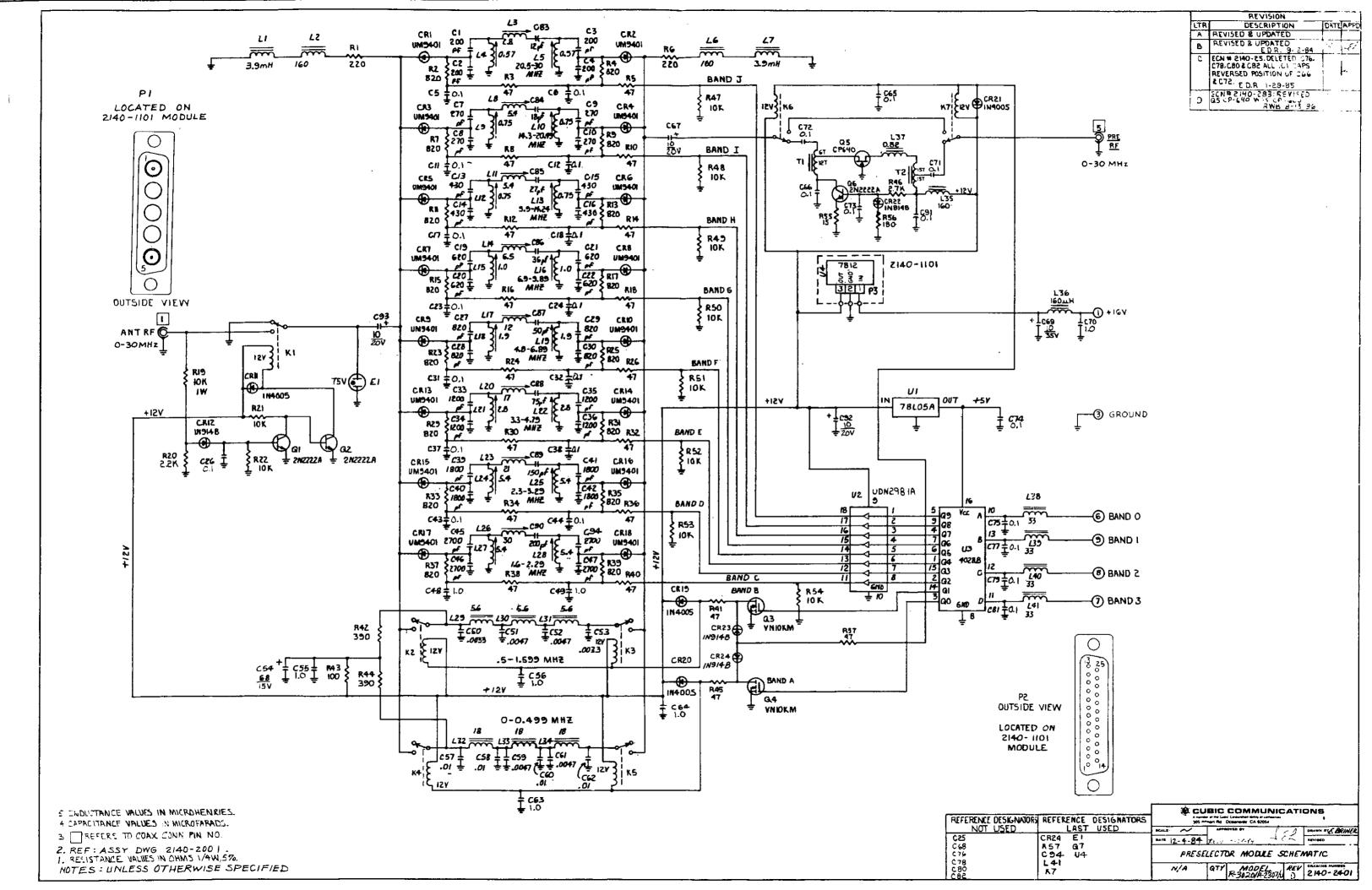

#### 2.1.4 Preselection

RF input filter in eight bands covering 1.6-30 MHz in approximate one half octave bands. Band selection automatic and switched by PIN diodes. Filter shape factor approximately 8 to 1. Filters used below 1.6 MHz relay switched for low signal distortion.

Frequency bands as follows:

| Band | Frequencies (MHz) | <u>Band</u> | Frequencies (MHz) |

|------|-------------------|-------------|-------------------|

|      |                   |             |                   |

| 1    | 0.000 to 0.4999   | 6           | 4.800 to 6.8999   |

| 2    | 0.500 to 1.5999   | 7           | 6.900 to 9.8999   |

| 3    | 1.600 to 2.2999   | 8           | 9.900 to 14.2999  |

| 4    | 2.300 to 3.2999   | 9           | 14.300 to 20.4999 |

| 5    | 3.300 to 4.7999   | 10          | 20.500 to 30.0000 |

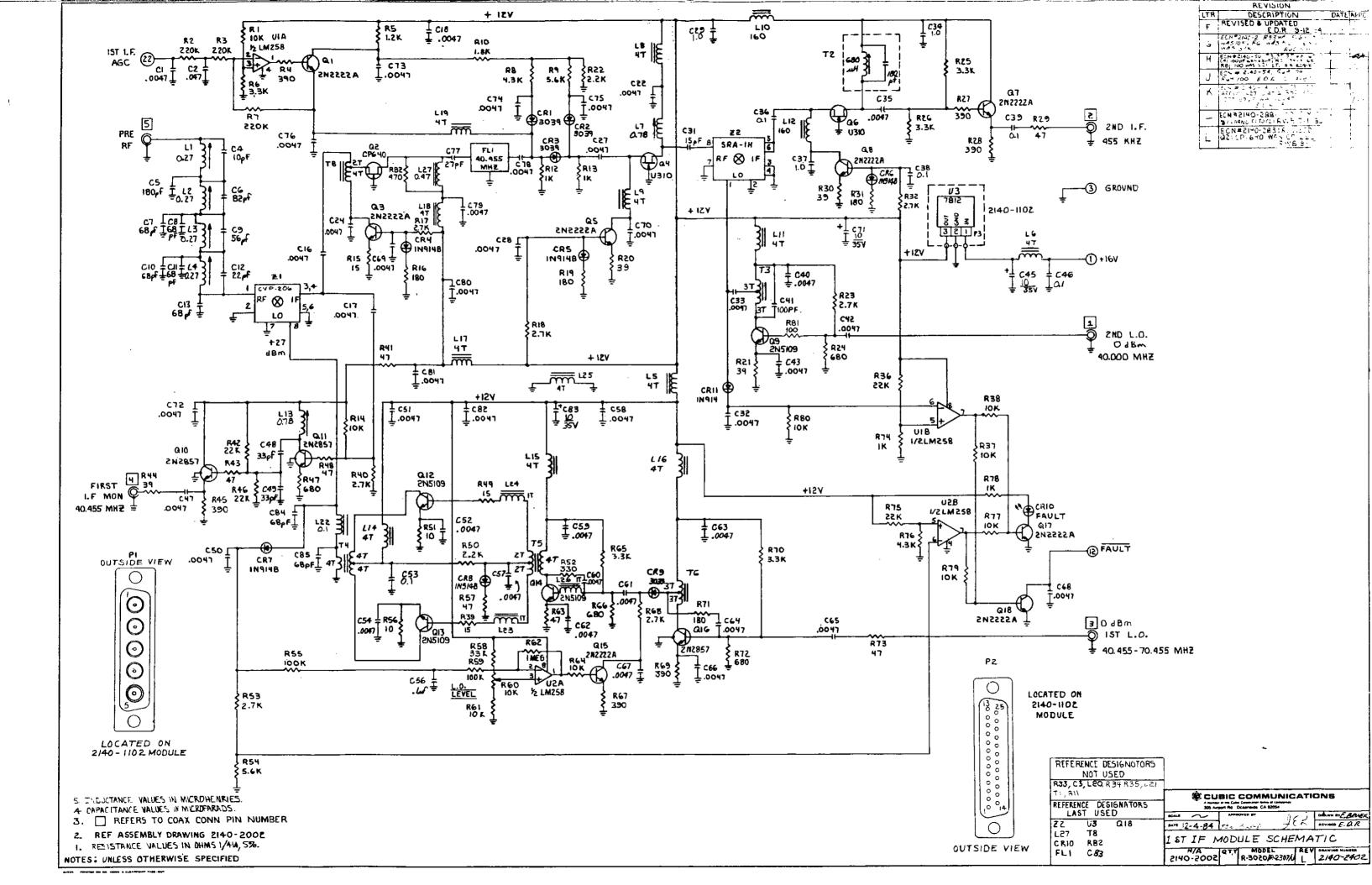

#### 2.1.5 IF Section

IF Frequencies

First IF: 40.455 MHz

Second IF: 455 kHz

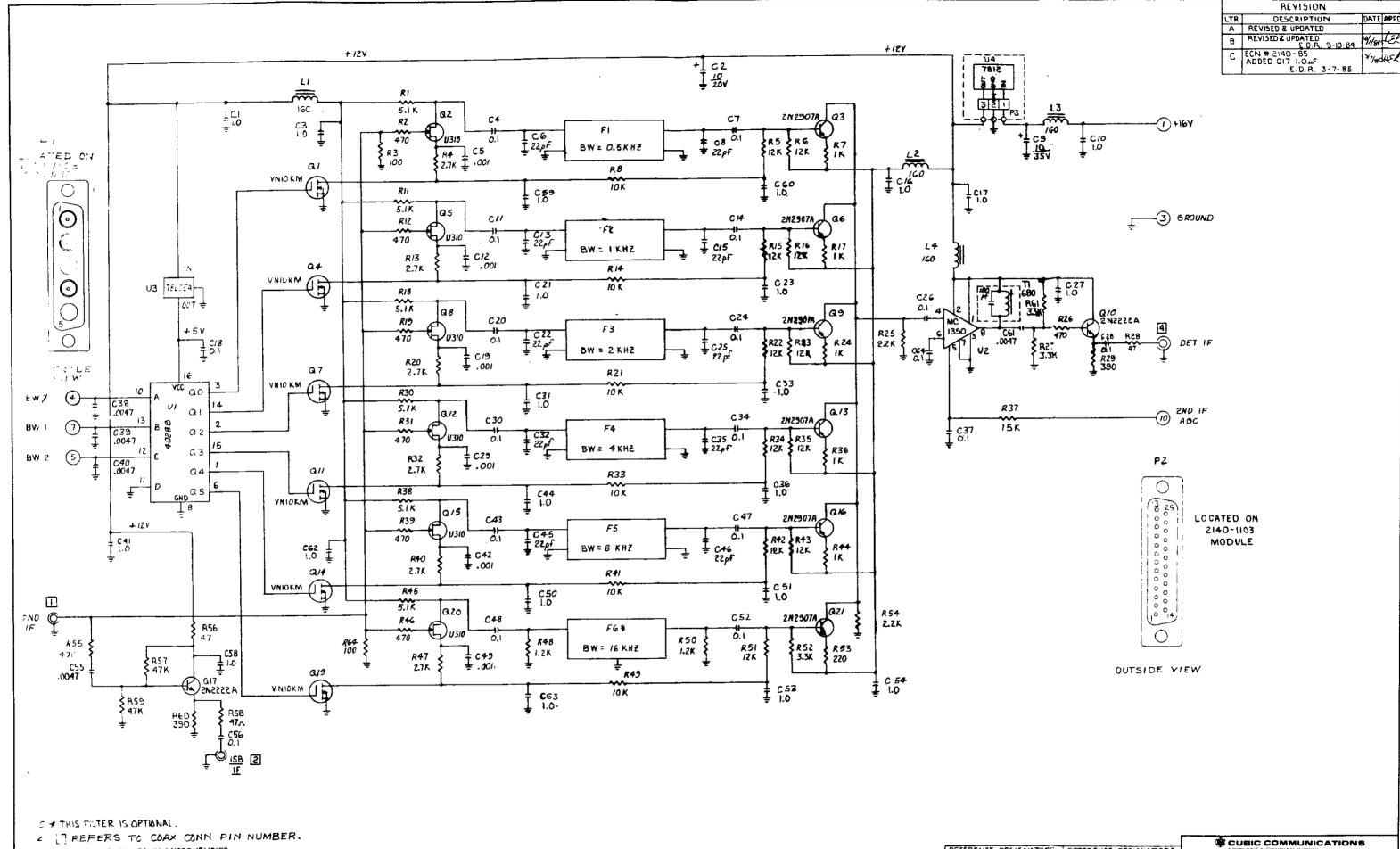

IF Bandwidth

First IF: 10 kHz or 20 kHz (Option)

Second IF: Selectable at time of order

Up to 5 of the following bandwidths

0.3 kHz 0.5 kHz 1.0 kHz 2.0 kHz

2.7 kHz (USB or LSB)

3.2 kHz 4.0 kHz 6.0 kHz 8.0 kHz

Optional 6th bandwidth 16 kHz

- RF derived in selected bandwidth. 2.1.6 AGC

- a. Fast attack, selectable hold, fast release

Attack Time

15 ms maximum

Hold Time (Selectable)

Zero Short

15 ms maximum 50 ms nominal 250 ms nominat

Medium Long

3 seconds nominal

Off

Remote gain control only

Release Time

200 ms maximum

b. Average type -- AM mode only using Envelope detector

Attack and release time constant 220 milliseconds nominal

AGC Range

120 dB minimum

AGC Threshold

0.5 uV (-6 dB audio reference level at 50 uV)

AGC Disable

Automatic Gain Control or Manual Gain Reduction

Manual Gain Control 0 to 127 dB gain reduction with AGC disabled

2.1.7 Interference Immunity

IF Rejection 100 dB typical

90 dB typical Image Rejection

Spurious Responses -130 dBm equivalent or less for -50 dBm input signals

-123 dBm input equivalent or less, 2 to 30 MHz Generated Spurious

Unmodulated wanted signal of 100uV together with a Cross Modulation

modulated (30% at 1 kHz) unwanted signal of 250mV spaced 100 kHz apart produces less than 10% cross

modulation of wanted signal.

Blocking Attenuation of a wanted RF signal of 50 uV and caused

by an unmodulated unwanted signal of 1V spaced 100

kHz away, less than 3 dB.

Inherent Oscillator

Re-radiation

1 uV, worst case from antenna connector into 50 Ohms.

Intermodulation

Distortion (typical)

The 3rd order I.M. products resulting from two input

signals at -20 dBm each less than -120 dBm.

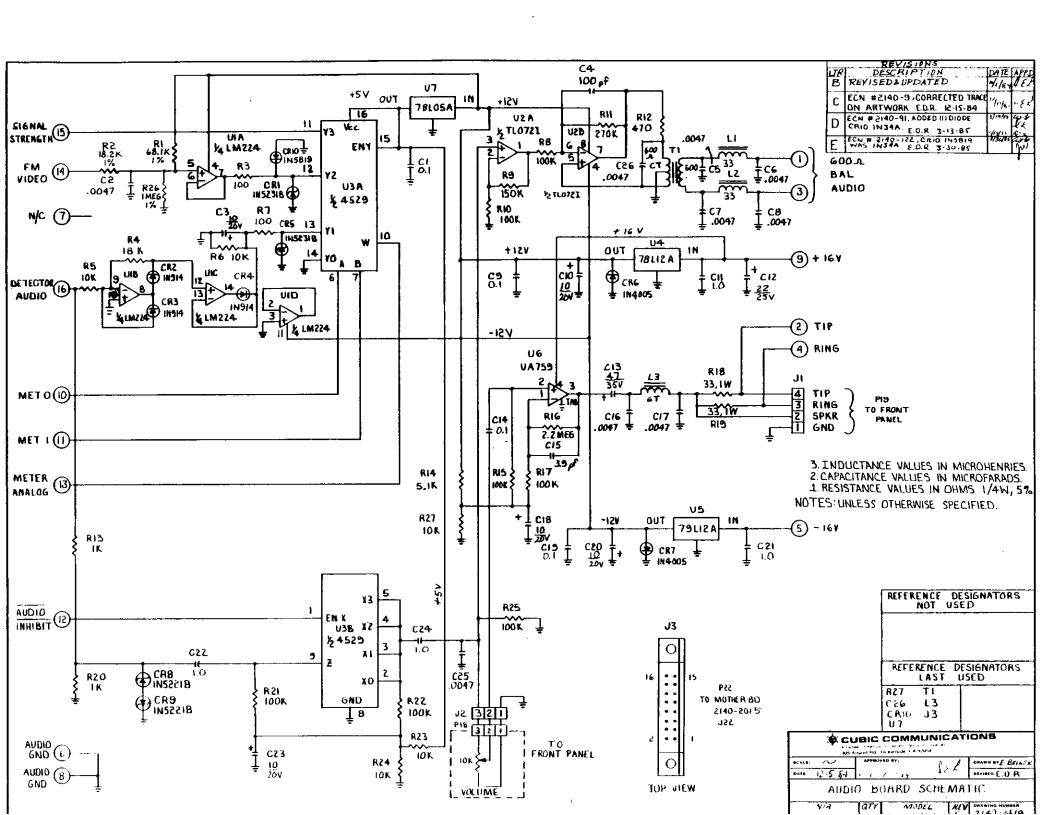

2.1.8 1/0 Signals

Outputs:

First IF (Wideband) 40.455 MHz with 1 MHz minimum bandwidth, 50 Ohms

at approximately 10 dB gain from input

455 kHz at selected bandwidth and nominal 0 dBm level Second IF (Selected)

$0 \pm 3$  dBm over AGC range (other IF optional)

O dBm. 50 ohm output, 1 or 10 MHz (Option) Synthesizer Reference

Audio

0 ±3 dBm, 600 ohms balanced (with AGC active) AM. CW, LSB or USB

.5 V/kHz AC coupled (4 V p-p maximum)

1 V per kHz (positive sense, DC coupled) FM Video

(always present) 93 ohm single ended

Signal Strength Digital format on bus

Analog voltages on AUDIO connector (0 to + 5 VDC)

Inputs:

50 mV minimum, 1 or 10 MHz (Option) Synthesizer Reference

Antenna Nominal 50 ohm input impedance

© CUBIC COMMUNICATIONS

R-3030/R-3080 TECH. MANUAL 2-3

#### 2.1.9 Remote Control via IEEE-488 or Serial Bus (One only)

#### 2.1.9.1 Receiver Functions

- a. Selected Frequency (10 Hz increments)

- b. Mode: LSB, USB, AM, CW, or FM

- c. IF Bandwidth (fixed as optioned in LSB or USB modes)

- d. BFO Frequency (± 9.99 kHz shift in 10 Hz steps)

- e. IF Shift ( $\pm$  9.99 kHz shift in 10 Hz steps)(fixed in LSB or USB modes)

- f. Automatic or Remote Gain Control

- q. AGC Hold Time (0, 50, 250, or 3000 msec) Note: AM selects average AGC

- h. IF Gain (0 to -127 dB reduction in 1 dB steps with AGC disabled)

- i. Setup of sweep step size and threshold offset in Sweep or Scan modes

- j. Start and Stop of Sweep and Scan Functions

Description

#### 2.1.9.2 IEEE-488 Bus Functions

Code

With the IEEE-488 interface module installed, the receiver implements the following IEEE-488 bus functions:

|                        |       | <del></del>                                                                      | •                                                                                                                                                                                               |  |  |

|------------------------|-------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SH1<br>AH1<br>T5<br>L3 |       |                                                                                  | Standard<br>Standard<br>No Extended Capability<br>No Extended Capability                                                                                                                        |  |  |

| SR1                    | Serv  | ice Request                                                                      | Rear Panel switchable SRQ enable                                                                                                                                                                |  |  |

| RL1                    |       | te. Local                                                                        | REM and GTO, no LLO                                                                                                                                                                             |  |  |

| DC 1                   |       | ce Clear                                                                         | Standard                                                                                                                                                                                        |  |  |

| DT 1                   | Devi  | ce Trigger                                                                       | Standard with GET command                                                                                                                                                                       |  |  |

| Interface              |       | Receivers contain<br>500 mV hysteresis.<br>capable of drivin<br>devices. Power u | er circuits are Bus compatible. Bus terminating resistors and have Drivers are three-state devices, g up to 15 other Bus compatible p/down protection is included to g invalid data to the Bus. |  |  |

| Format                 |       |                                                                                  | t data and eight for control status<br>nsfer is byte serial using a three-<br>IEEE-488 Standard.                                                                                                |  |  |

| Transfer               | Rates |                                                                                  | s is typically 11K bytes/sec when s/sec when listening.                                                                                                                                         |  |  |

Comments

#### 2.1.9.3 Serial Bus Functions

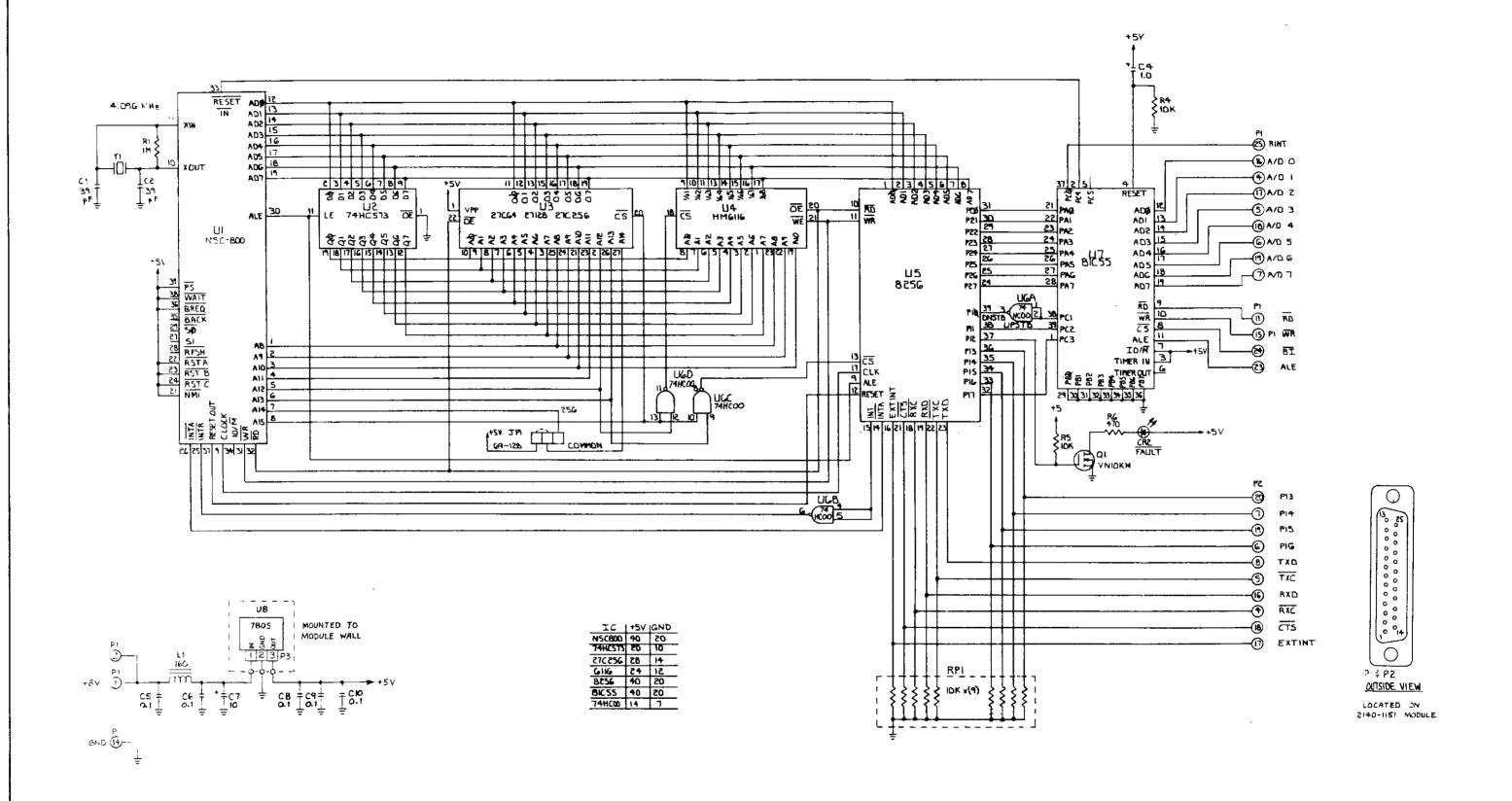

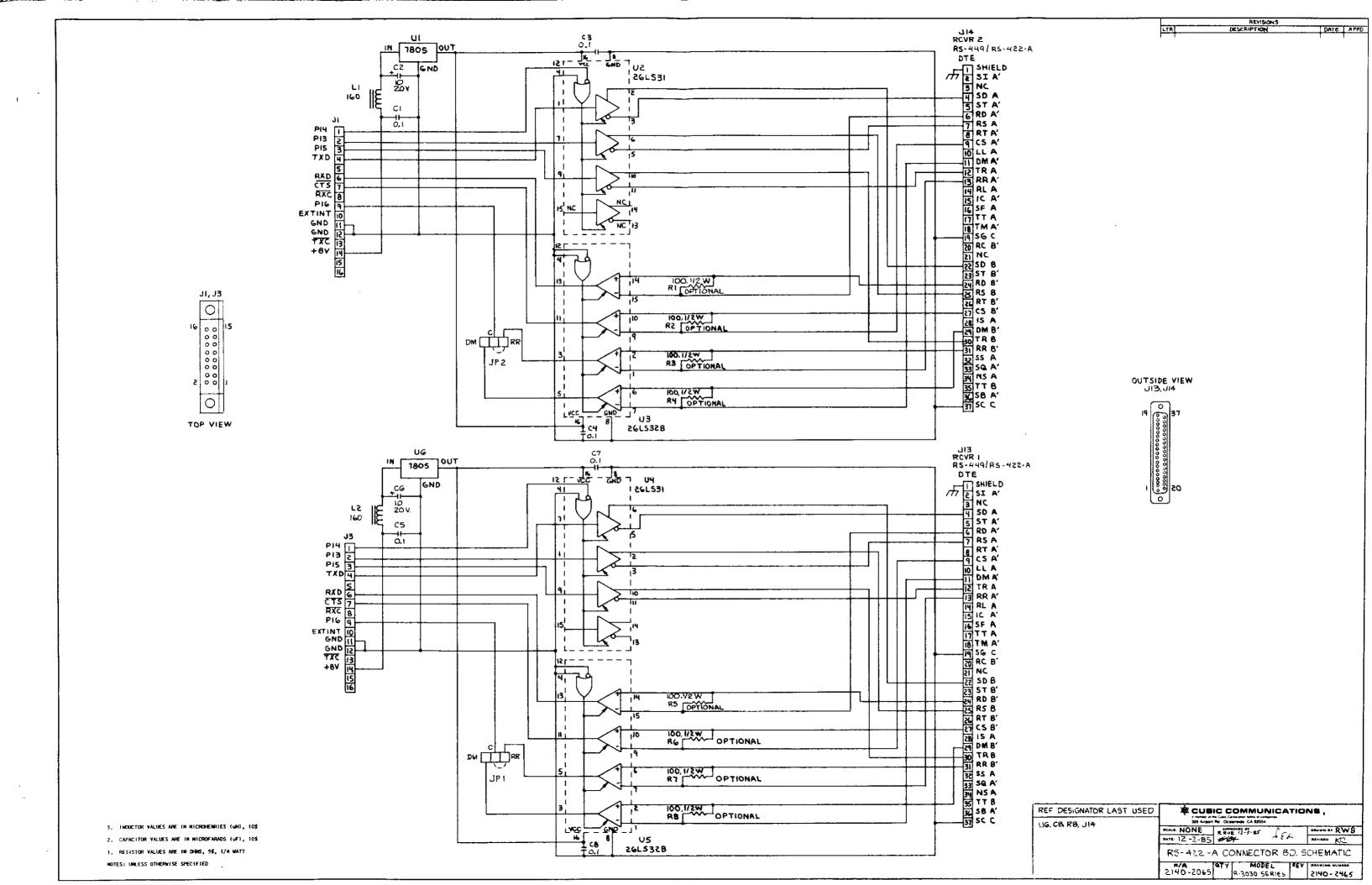

The serial bus interface module is capabile of communicating in all normal serial asychronous modes. A separate serial bus connector plate and adapter board is required for each type of bus. At the time of publication of this issue of the manual, the following buses are available:

RS-232C, single drop

RS-422A/RS-449, multiple drop

R-3030/R-3080 TECH. MANUAL 2-4

### 2.1.9.3 <u>Serial Bus Functions and Description</u>

With the serial bus interface module and appropriate bus connector board installed, the receiver may be controlled in all normal functions. A different serial bus connector board is required for each type of bus.

Depending on the type of connector board installed in the receivers, a number of different serial data buses may be accommodated. These may include the EIA RS-232, EIA RS-422, EIA RS-423, EIA RS-485, or MIL-STD-188 as required by the application. These specifications do not actually call out a bus structure but only a method of signalling on a set of wires. Unlike the IEEE-488 standard, all messages must be defined for the unit being controlled and do not follow any bus protocol except for that defined by the equipment.

RS-232

The RS-232 bus is an unbalanced bus capable of signalling over short distances and with limited data rates. This bus is ordinarily used over distances of up to 50 feet with a single controller and single controlled device. This bus uses two single wires (one for each direction of transmission) and ground and is generally found to be disturbed by noise or other common mode signals with over distances greater than a few meters.

MIL-STD-188C

The MIL-STD-188C bus is similar to the RS-232 bus except for a more limited voltage swing (+ and - 5 to 7 volts instead of + and - 5 to 15 volts) and for the fact that the mark and space conditions are defined opposite to the RS-232 standard. The same limitations on the use of the RS-232 apply to the MIL-STD-188C bus.

MIL-STD-188-114 (Unbalanced)

This bus is similar to the other unbalanced buses discussed above except that the standard requires a differential bus receiver to sense signal against the ground lead and hence allows for transmission over distances of up to 4000 feet (with a baud rate less than 1000). Transmission at rates up to 100 K Baud are recognized with cable lengths no longer than 40 feet. As with the other unbalanced buses, the signal path consists of a single wire for each direction of transmission plus a common signal ground wire. The output signal swings are limited to + and - 4 to 6 volts around signal ground. This standard allows for up to 10 receivers with a single driver.

RS-423

This bus is similar to the MIL-STD-188-144 (Unbalanced) bus except that controlled linear wave shaping allows signalling at rates of up to 9000 baud for 4000 feet of cable. Waveshaping with RC time constants limits the baud rate to 3000 for 4000 feet of cable and the maximum baud rate is limited under any condition to 100 K baud. As with all unbalanced buses, common mode noise can be a serious problem with long cable runs in the presence of other electrical noise sources and usually provides a baud rate and cable length limit much less than that listed above. This standard allows for up to 10 receivers with a single driver.

## **©CUBIC COMMUNICATIONS**

MIL-STD-188-114 (Balanced)

This is a balanced bus with signalling being performed by the differential voltage between two wires and in the presence of relatively large common mode voltages. A separate pair of wires is used for each direction of data transmission for this and for the other balanced buses. Signalling is allowed at rates of up to 100 K baud with cable length of 4000 feet with rates of up to 10 M baud with cable length of 40 feet. Exceptional rejection of common mode noise results from this bus configuration. This standard allows for up to 10 receivers with a single driver.

RS-422

This is a balanced bus essentially identical to the MIL-STD-188-114 (Balanced) bus discussed above. This standard allows for up to 10 receivers with a single driver. Some systems have been implemented with a larger number of bus receivers.

RS-485

The RS-485 bus is the only bus defined that allows for multiple bus transmitters or drivers. The standard allows for up to 32 drivers and 32 receivers on the bus. The bus receivers are high impedance under all conditions (including power off) while the bus transmitters are high impedance until commanded to transmit. This bus is otherwise similar to the RS-422 and MIL-STD-188+114 (Balanced) bus and shares similar characteristics.

A summary of the various bus characteristics is presented below:

| SPEC.                                                         | EIA<br>RS-232              | EIA<br>RS-423                   |                              |                | MIL-STD<br>-188-114<br>SEC. 5.1  |                                                    | EIA<br>RS-485                                       |                              |

|---------------------------------------------------------------|----------------------------|---------------------------------|------------------------------|----------------|----------------------------------|----------------------------------------------------|-----------------------------------------------------|------------------------------|

| MODE DRIVERS RECEIVER: MAX LEN. @ RATE MAX RATE @ LENGTH MARK | NO SPEC<br>NO SPEC<br>20 K | 1<br>10<br>4000<br>3 K<br>100 K | 1<br>1<br>NO SPEC<br>NO SPEC |                |                                  | BALANCED<br>1<br>10<br>4000<br>100 K<br>10 M<br>40 | BALANCED<br>32<br>32<br>4000<br>100 K<br>10 M<br>40 | feet<br>Baud<br>Baud<br>feet |

| MIN OUT<br>MAX OUT<br>LOAD RES<br>OFF RES                     | +/-15V                     | +/-3.6V<br>+/-6V                | +/-5V<br>+/-7V<br>NO SPEC    | +/-6V          | +/-2V<br>+/-6V<br>90 min<br>60 K | +/ <b>-</b> 6V                                     | +/-1.5V<br>60 min<br>120 K                          | Ohms<br>Ohms                 |

| SENS.                                                         | 3-7 K                      | 4 K min<br>+/2V                 | ERISTICS: 6 K min +/6V N/A   | +/ <b>-</b> 3V | 4 K min<br>+/2V<br>+/- 7V        | +/ <b>-</b> .2V                                    |                                                     | ı Ohms                       |

#### 2.1.10 Front Panel Keypad Control Functions

The following functions on the receiver are controlled from the front panel keypad. Some keys are single function while others share a numeric entry key.

#### 2.1.10.1 Single Function Keys

- STO Saves current frequency, mode, bandwidth, BFO offset, IF Shift, AGC hold time, manual gain setting, channel lockout (skip) flag, scan threshold, sweep step size, and scan dwell time in designated channel.

- RCL Puts frequency, mode, bandwidth, and AGC hold time from designated channel memory in display. Recalls also BFO offset, IF Shift, AGC hold time, and manual gain setting for use by receiver if ENTER key pressed. Recalls channel lockout (skip) flag, scan threshold, and scan dwell time for resetting if desired.

- CAN Cancels current keypad operations (before ENT key press), returns unit to previous state. Disables knob control changes.

- ENT Causes current displayed frequency, mode, bandwidth, BFO offset, IF Shift, AGC hold time, manual gain setting, and signal threshold to be programmed into receiver. Disables knob control of numerical functions.

- SCAN Starts scan of memory channels from channel recalled and entered to channel recalled just before SCAN key press at approximately 50 channels per second (20 msec per channel). Uses frequency, mode, bandwidth, BFO offset, IF Shift, AGC hold time, and manual gain setting from memory. Omits any channel with skip flag set. Pauses on each frequency for a time period adjustable by main adjustment knob. Stops scan on channel with signal above programmed and stored threshold for programmed and stored dwell time.

- SWP Starts sweep of frequency bands determined by parameters in memory channels. May sweep one band selected by even numbered channel recalled and entered sweeping to frequency stored in next higher odd numbered channel or all bands from odd numbered channel recalled and entered to channel recalled just before SWP key press.

Starting with first frequency in even numbered channel for sweep, uses frequency, mode, bandwidth, BFO offset, IF Shift, AGC hold time, and manual gain setting from memory. Sweep increment is set by stored step size and frequency is changes at approximately 50 frequencies per second. Pauses on each frequency for a time period adjustable by main adjustment knob. Halts sweep on frequency with signal above programmed and stored threshold for programmed and stored dwell time then continues sweep. Stops sweep at frequency stored in next odd numbered channel, then restarts sweep under control of frequency and other parameters stored in next even numbered channel. Contines with sweep parameters set by even numbered channels and stop frequency set by frequency in odd numbered channels. Omits any sweep range designated by skip flag set in even numbered channel.

member of the Tub III of the 19th

- STOP/ Causes SCAN or SWEEP to stop on current channel or frequency. Allows adjustment of any receiver parameter while stopped. Causes stopped SCAN or SWEEP to be continued from current channel or frequency.

- METR Alternate press toggle the meter between signal strength, audio, and frequency.

#### 2.1.10.2 Keys That Open the Numeric Function

- FREQ Allows adjustment of frequency by adjustment knob. If numeric key pressed, allows keypad entry of frequency. Enter key terminates numeric entry. Display indicates "Fr" and frequency of RF input (7 digits plus decimal point at MHz).

- Allows adjustment of BFO offset by adjustment knob. If numeric key pressed, allows keypad entry of offset frequency. Enter key terminates numeric entry. Display indicates "bF" and offset frequency of BFO (3 digits plus sign plus decimal point at kHz).

- IF Allows adjustment of IF shift by adjustment knob. If numeric key pressed, allows keypad entry of shift frequency. Enter key terminates numeric entry. Display indicates "IF" and shift frequency of IF (3 digits plus sign plus decimal point at kHz).

- GAIN Allows adjustment of RF gain by adjustment knob. If numeric key pressed, allows keypad entry of RF gain. Enter key terminates numeric entry. Display indicates "GA" and RF gain reduction in dB (3 digits).

- LEVL Allows adjustment of threshold level for scan or sweep stop by (5) adjustment knob. If numeric key pressed, allows keypad entry of threshold level. Enter key terminates numeric entry. Display indicates "L" and threshold level in dBm (3 digits).

- OWEL Allows adjustment of time for dwell during scan or sweep operations when signal is sensed to be above programmed threshold by adjustment knob. If numeric key pressed, allows keypad entry of dwell time. Enter key terminates numeric entry. Display indicates "d" and dwell time in seconds (1 digit).

- STEP Allows adjustment of step size used in frequency sweep. Minus sign (-) used for BFO offset, IF shift, and threshold offset only.

- 2.1.10.3 <u>Sequential Function Keys</u> (Numeric function not opened)

- MODE Sequences mode selection between LSB, USB, AM, FM, and CW.

(7) Indicated by single letter on mode display (L, U, A, F, or C)

- BW Sequences IF bandwidth between filters installed.

- (8) Approximate bandwidth indicated on display.

- AGC Sequences AGC hold time between zero, 0.05, 0.25, 3.0 seconds and off.

- (9) (Manual gain control only in off position). Indicated by numbers indicating approximate hold time. Blank when AGC disabled (off).

- RATE Sequences tuning rate between 10 Hz, 100 Hz, and 1 kHz per step or 1 dB per step on main adjustment knob and adjustment knob lock. Rate indicated by intensifying significant digit in main display. Knob lock indicated by not intensifying digit.

- SKIP Alternate presses toggle the channel skip flag used during scan of (.) memory channels. Indicated by SKIP annunciator.

#### 2.1.11 Front Panel Displays

The following parameters are displayed on the front panel of the receiver. All functions are for each receiver in a 2 receiver assembly.

- FUNCTION DISPLAY Two alphanumeric characters -- 00 through 99 for store or recall, F for frequency, bF for BFO offset, IF for IF shift, GA for Gain, L for threshold level, d for dwell time, SE for step size adjustment, OF for threshold offset adjustment, blank otherwise.

- MAIN DISPLAY Seven digits numeric plus decimal points and minus sign. Used for the following functions:

FREQUENCY -- 7 digits plus . at MHz -- normal display

BFO Offset -- sign (blank or -) plus 3 digits and . at kHz -- displayed during BFO offset adjustment only.

IF Shift -- sign (blank or -) plus 3 digits and . at kHz -- displayed during IF shift adjustment only.

RF GAIN -- minus sign plus 3 digits -- displayed during RF gain adjustment only

THRESHOLD -- minus sign plus 3 digits -- displayed during threshold adjustment only.

DWELL TIME -- 1 digit -- displayed during dwell time adjust only

MODE DISPLAY Single character -- L, U, A, C, or F

- BANDWIDTH Two characters plus decimal point indicating approximate bandwidth in kHz -- set by option configuration

- AGC DISPLAY Two digits plus decimal point indicating approximate hold time in seconds (.00, .05, .25, 3.0, or blank for MGC only)

#### ANNUNC LATORS

AUDIO indicates that meter reads mode selected audio level

FREQ indicates that meter reads relative frequency

REM indicates that control of unit is via remote control bus

FAULT indicates an internal detected fault

KPAD indicates keypad entry is active, display does not

necessarily indicate current frequency.

SKIP indicates channel is skipped during scan operations

METER; 20 segment light bar meter, calibrated from -120 to 0 dBm for signal strength, -35 to + 4 dBm for audio, -50% to + 50% of IF BW for frequency.

#### 2.1.12 Other Front Panel Controls and Functions

POWER ON/OFF SWITCH -- toggle type circuit breaker

LOCAL/REMOTE SWITCH -- small toggle switch for taking positive local control or allowing remote control function (Not IEEE-488 standard).

MAIN ADJUSTMENT KNOB -- 1.75 inch diameter knob on optical shaft encoder

VOLUME -- Adjusts audio level to phones jack tip and ring contacts

PHONES JACK -- Tip and ring contacts driven independently by selected mode audio. Series resistor in each circuit to protect amplifier from short circuit due to use of single circuit phone plug.

#### 2.1.13 Rear Panel Controls

Reference Selector -- One Internal/External switch per assembly.

Address Selector (IEEE-488 only) -- 8 individual 2-position switches for selecting individual bus addresses and talker only, listener only, and SRO enable functions. The R-3030 has 2 such groups of switches, the R-3080 only one.

#### 2.1.14 Connectors (all on rear panel)

RF Antenna TNC or BNC (Option) Female

IF First IF TNC or BNC (Option) Female

IF Second IF TNC or BNC (Option) Female

REF Reference In TNC or BNC (Option) Female

REF Reference Out TNC or BNC (Option) Female

REMOTE CONTROL

IEEE-488 BUS (24 cont.) Amphenol Blue Ribbon IEEE-488 stacking connector

or

RS-232C DB-25P on chassis, mates with DB-25S

or

RS-422/RS-449 DC-37P on chassis, mates with DC-37S

AUD10

12 contact MIL crimp MS3122A14-92P or Burndy G2B14-92PNH

on chassis, mates with cable connector

or MS3126F14-92S or Burndy G6F14-92SNH

19 Contact MIL solder MS3112E-14-19S on chassis, mates with cable conn.

MS3116F-14-19P

or

15 contact D DA-15S on chassis, mates with DA-15P

POWER

4 contact MIL crimp MS3122A10-4P or Burndy G2B10-4PNH

on chassis, mates with cable connector

MS3126F10-4S or Burndy G6F10-4SNH

or (Line on pins A and C, Ground on Pins B and D)

3 contact commercial CEE 22 Form VI (3 pin)

PHONE JACKS Rear panel 1/4 inch phone jacks connected in parallel

with front panel phone jacks

#### 2.1.15 Running Time Meter

Each receiver has a 0 to 9999 hour running time meter installed. This meter operates whenever the front panel power switch is turned on and the unit is connected to AC power. The meter is mounted on the rear panel and visible from the rear of the unit.

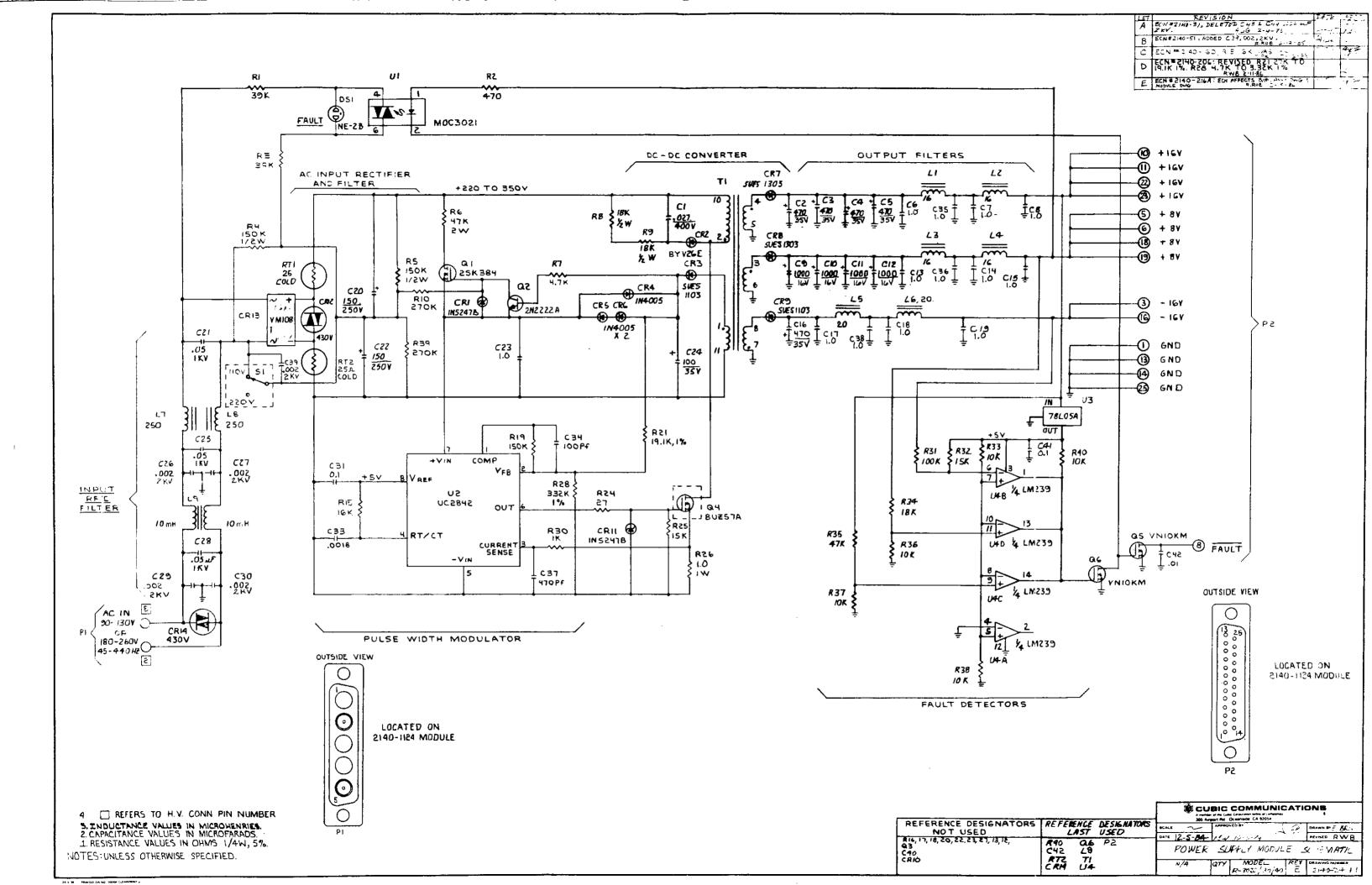

#### 2.1.16 Power Requirements

100 - 130 VAC or 200 - 260 VAC (selectable) 47-420 Hz, 40 watts maximum per receiver.

## **© CUBIC COMMUNICATIONS**

#### 2.2 ENVIRONMENTAL CONDITIONS

#### 2.2.1 Temperature

-20 °C to +60 °C Operating -40 °C to +70 °C Storage

Tested to MID-STD-810D, Method 501.2, Table 501.2-111 and MIL-STD-810D, Method 501.2, Table 2.2-1.

#### 2.2.2 Relative Humidity

Humidity test per MIL-STD-810D, Method 507.2, Procedure 1, Temperature 50°C, Figure 507.2-1, 5 total cycles.

#### 2.2.3 Shock and Vibration

Shock per MIL-STD-810D, Method 516.3 Figure 516.3-4 20g 11 ms sawtooth, 30g 11 ms in one axis

High impact shock per MIL-S-910C.

Vibration per MIL-STD-810d, Method 514.3, Figure 514.3-36  $W_0 = .003g^2/Hz$  (Random)

## 2.2.4 <u>Electromagnetic Emission and Susceptibility</u>

In conformance with the applicable provisions of MIL-STD-461B, class A1a as applicable to Navy and Air Force procurements.

Filtering in conformance with MIL-STD-461B, section 4.2.1.

Requirements per MIL-STD-461B as follows:

- CE01 Conducted Emissions, Power and Interconnecting Leads, Low Frequency (up to 15 kHz)

- CE03 Conducted Emissions, Power and Interconnecting Leads, 0.015 to 50 MHz

- CE07 Conducted Emissions, Power Leads, Spikes, Time Domain

- CS01 Conducted Susceptibility, Power Leads 30 Hz to 50 kHz

- CS02 Conducted Susceptibility, Power Leads 0.05 to 400 MHz

- CS06 Conducted Susceptibility, Spikes, Power Leads

- RE01 Radiated Emissions, Magnetic Field, 0.03 to 50 kHz

- RE02 Radiated Emissions, Electric Field, 14 kHz to 10 GHz

- RS01 Radiated Susceptibility, Magnetic Field, 0.03 to 50 kHz

- RS02 Radiated Susceptibility, Magnetic Induction Field, Spikes and Power Frequencies

- RS03 Radiated Susceptibility, Electric Field, 14 kHz to 40 GHz

### **<b>©** CUBIC COMMUNICATIONS

#### 2.3 PHYSICAL CHARACTERISTICS

#### 2.3.1 Construction

All chassis and module assemblies use chem-film treated aluminum alloy and stainless steel hardware in accordance with the provisions of sections 3.4.9.13 and 3.4.11.2 (j) of MIL-E-16400. No steel or other materials subject to destructive corrosion are used.

The front panel is painted with semi-gloss light gray enamel in accordance with the requirements of MIL-E-15090, Class 2, Type II or Type III, color number 26307 of FED-STD-595, with black legends and handles. Finish of all painted surfaces is in accordance with the provisions of section 3.4.11.3 of MIL-E-16400.

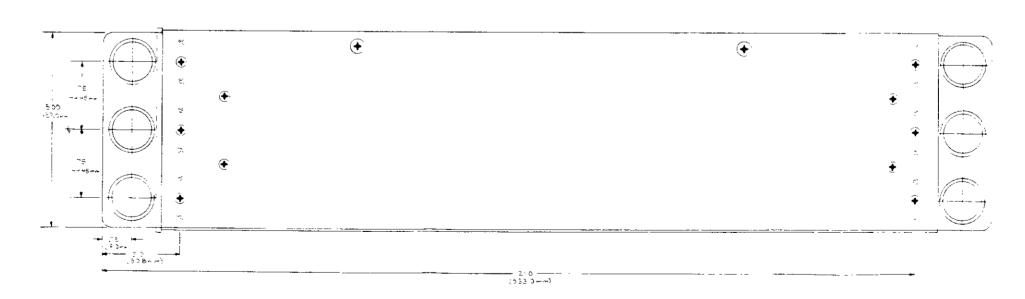

#### 2.3.2 Maintainability

Access to replaceable module assemblies is by means of 1/4 turn captive fastners. Modules are secured with 1/4 turn captive fasteners. Correct module position in assembly indicated by a diagonal stripe on the module top surfaces.

#### 2.3.3 <u>Size</u>

R-3030

Modules for two complete receivers are packaged in one standard 5.25 inch high by 19 inch wide rack panel and chassis with provisions for mounting slides. Slides are furnished if specified on the purchase order. Recommended slide is Chassis-Trak model C-300-S-118, Option Revision C (single hole mounting).

R-3080

Modules for one receiver are packaged in one 5.25 inch high by 8.4 inch wide chassis designed for side-by-side mounting with similarly sized equipment to make a standard rack chassis configuration. Attaching hardware and rack angles furnished if specified on the purchase order.

Depth, including protective handles, is approximately 21.2" behind the front panel. Connectors on the rear panel are inside the handle dimensions and are protected by the handles and chassis from contact with any flat surface large enough to contact both handles simultaneously at any angle of contact. The rear handles of the R-3030 include a receptacle for a standard ATR tapered locating pin. One pair of Barry 3098-005-000 pins furnished with each 2-receiver assembly.

#### 2.3.4 Weight

R-3030

Approximately 47 pounds for one chassis containing modules for two receivers not including mounting slides (optional items).

R-3080

Approximately 25 pounds for one chassis containing modules for one receiver.

## **©** CUBIC COMMUNICATIONS

## 2.3.5 Reliability

The calculated Mean Time Between Failures is approximately 5000 hours per receiver unit when calculated using the methods and failure rates of MIL-HDBK-217D with failure rates of unrated components calculated using the methods of MIL-HDBK-217D.

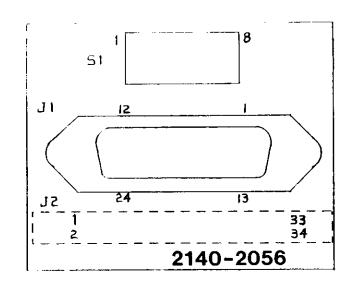

FIGURE 2-1

R-3030 OUTLINE AND MOUNTING

© CUBIC COMMUNICATIONS

R-3030/R-3080 TECH. MANUAL 2-15

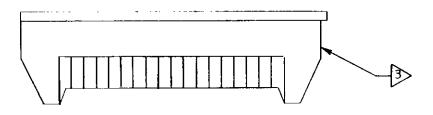

FIGURE 2-2 R-3080 OUTLINE AND MOUNTING

CUBIC COMMUNICATIONS

A member of the Cubic Corporation family of companies

R-3030/R-3080 TECH. MANUAL 2-16

#### 3.0 INSTALLATION

#### 3.1 UNPACKING AND INSPECTION

Examine the shipping carton for damage before unpacking the unit. If the carton is damaged, open the carton in the presence of an agent of the shipping carrier if possible. If the carton is not damaged, retain the carton and packing materials for inspection if damage is found after the unit is unpacked.

Open the carton and remove the foam packing material on top of the unit. Lift the unit free of the carton. No packing materials are required or provided inside the unit. Replace the foam packing material in the carton. The carton may be saved for possible re-shipment if required.

Upon unpacking, inspect the unit for obvious external damage. Pay particular attention to dents or bent sheetmetal. If damage is evident, remove the top and bottom covers of the unit and inspect for further damage such as modules removed from their mounts or damaged circuit boards. Do not attempt to operate the unit if such damage is noted until further checks are made.

#### 3.2 MOUNTING

The unit is designed for table top or rack panel mounting in a fixed or mobile environment in a relatively protected location. The unit is not water proof but is considered dustproof and will withstand normal interior exposure.

#### R-3030

If slide mounting is to be used, securely mount the outer section of the slides to the rack cabinet being sure to select the correct mounting holes for the front flanges and the rear brackets. Before tightening the mounting screws securely, slide the chassis assembly into the rack mounted portion of the slides and adjust the hardware position as required for a smooth siding fit. Securely tighten all hardware. After securing all cables to the rear of the unit, insure that the proper 10-32 screws are used to secure the panel of the receiver assembly to the rack.

#### R-3080

If the unit is to be installed together with other equipment in a full rack width configuration, secure the two units together using the inserts for the handle holes. Insert the threaded fasteners and tighten securely. Slides are not used in this configuration.

If the unit is not to be mounted on chassis slides, insure that a suitable shelf or angle bracket is used to support the weight of the unit and that the unit is suitably braced to prevent movement in the event of motion of the vehicle or platform in which it is installed. If it is not installed in a vehicle or other mobile platform, it may not be necessary to brace the unit against movement. The weight of the unit must, however, be adaquately supported.

CAUTION: DO NOT SUPPORT THE WEIGHT OF THE UNIT BY THE FRONT PANEL ONLY. USE CHASSIS SLIDES OR A SUITABLE SUPPORT SHELF

## & CUBIC COMMUNICATIONS

#### 3.3 POWER

The unit is powered from either a source of 100 to 130 VAC or 200 to 260 VAC, 47 to 400 Hz. One power connector is used per two receiver assembly (R-3030) and each receiver has its own power control circuit breaker.

The AC power connector (J1) may be a military standard type having crimp type male contacts or a international standard commercial type depending on the option ordered. The power cable has the socket type contacts. On the military style connector, pins A and C are used for the AC line while pin B is used for ground. If the power cable used is the shielded type, pin D may be used for the shield. Both pins B and D are connected to chassis ground.

A mating cord set is provided having a U.S.A. standard 3 pin plug for 115V service. Should a different plug be required, either cut off the U.S.A. standard plug and replace it with the desired plug or replace the cord set. The U.S.A. standard cord uses the black wire for the AC line live side, the white wire for the AC line neutral, and the green wire for chassis ground. Only the green wire is connected to the chassis. International color code for these functions uses a brown wire for the AC line live side, a light blue wire for the AC line neutral, and a green wire with a yellow tracer for the chassis ground. Either type of color code may be found in the power cable.

The unit will normally be marked with the line voltage for which it was set at the factory if the factory setting was for 220 VAC operation. Unless otherwise specified, the unit will be set to be operated from a source of 110 VAC. If the line voltage available is not as marked or if there is some doubt as to how the unit is set, remove the top cover of the assembly by undoing the 1/4 turn captive fasteners. The power supply modules are in the rear of the assembly.

Determine the AC line voltage available. If it is in the range of 100 to 130V, set the rotary switch on the power supply module to the 110V position. If the available line voltage is in the 200 to 260V range, set the rotary switches to the 220V position.

CAUTION: BE SURE THAT THE VOLTAGE SELECTOR SWITCH IS SET TO THE CORRECT POSITION FOR THE LINE VOLTAGE AVAILABLE FOR BOTH RECEIVERS IN THE R-3030 TWO-RECEIVER ASSEMBLY.

#### 3.4 ANTENNA

R-3030

Connect the antennas to be used to the ANTENNA receptacles on the rear panel. A separate antenna connection is made to each receiver in the assembly. As viewed from the rear of the chassis, the antenna connector on the left (J3) is connected to the receiver chassis on the left while J4 is connected to the receiver on the right. This means that the receiver connected to the antenna via J4 is controlled from the left side of the front panel and vice versa. (Front to back reverses right and left) The impedance presented to the antenna will be approximately 50 ohms with a VSWR of less than 3 to 1.

R-3080

The R-3080 has only one antenna receptacle. Connect the antenna to be used.

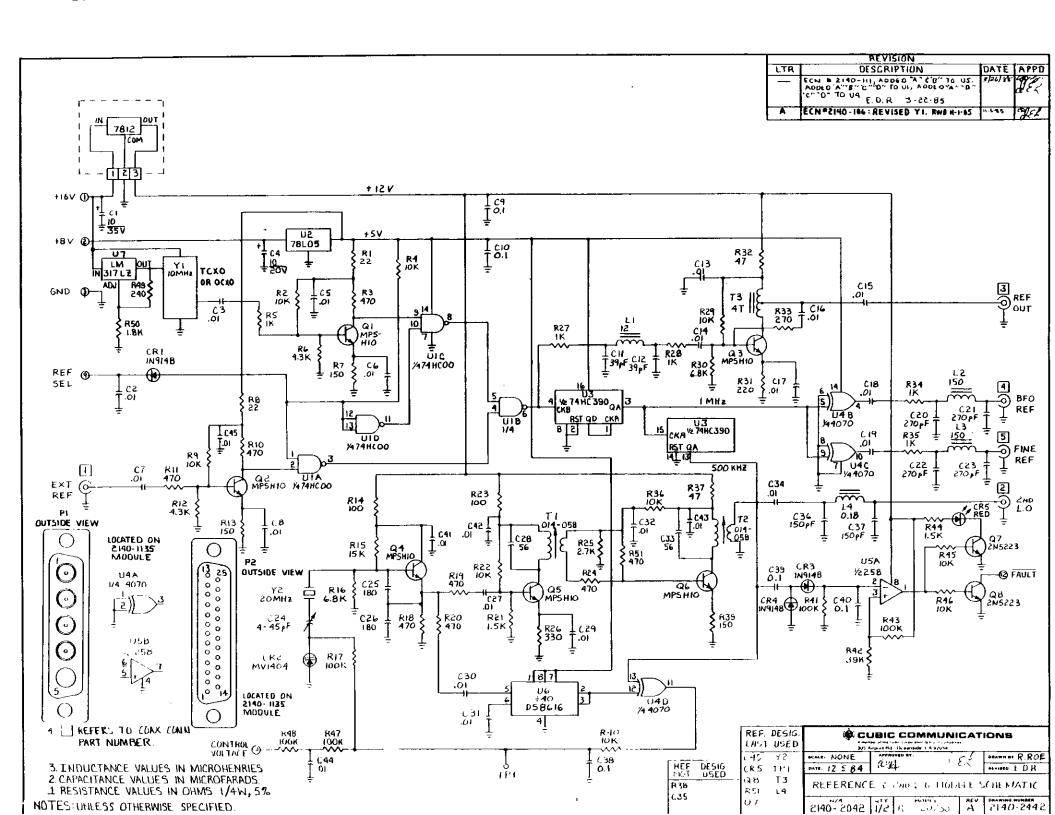

#### 3.5 FREQUENCY STANDARD

The unit is designed to use either its internal frequency standard or an external frequency standard where very high accuracy is required. The internal frequency standard provides an overall frequency accuracy of approximately 1 part per million (30 Hz at the highest frequency). On special order, an internal oven stabilized crystal oscillator having an overall frequency accuracy of 0.1 parts per million may be installed in the Reference and 2nd L.O. module.

#### R-3030

With the rear panel REF SELECT switch set to the INT position, the rear panel REFERENCE OUT receptacle (J10) will provide an output from the internal standard in receiver number 2 (right side as viewed from the rear, left side as viewed from the front) for frequency measurement or other uses. Output frequency is optionally 1 or 10 MHz and is approximately a sine wave. Output level is approximately 0.6V peak-to-peak and the unit can deliver this voltage into a 50 ohm load.

#### R-3030

With the rear panel REF SELECT switch set to the EXT position, the rear panel REFERENCE IN receptacle (J9) will accept an input from an external frequency standard. The unit will require a sine or square wave at 10 MHz (optionally 1 MHz) with a level of 0.1V to 2V peak-to-peak. Input impedance is approximately 1K ohms. The signal from the external frequency standard will be repeated on the REFERENCE OUT receptacle (J10) at the same level as the internal frequency standard. NOTE: When operating from an external standard, both receivers must be turned on to insure proper operation.

#### R-3080

The reference input and output connections to the R-3080 are similar except, of course, only one receiver and reference oscillator is present.

Set the INT/EXT selector switch to the desired position. If required, connect coaxial cables from the frequency standard receptacles to a frequency measuring device, another receiver, or an external frequency standard as required.

#### 3.6 WIDEBAND 1st IF MONITOR OUTPUT

A wideband 1st IF MON(itor) output from each receiver in the assembly is available on separate rear panel receptacles. This signal is centered at 40.455 MHz with a bandwidth of approximately 1 MHz. The signal level at this output is approximately 10 dB larger than the signal level into the antenna input. This output may be used for wideband reception modes or connected to a suitable spectrum analyzer. As with the ANTENNA connectors, the connector on the left (J5) is connected to the receiver on the left and vice versa for J6. The R-3080 has only one such connector.

#### 3.7 2nd IF MONITOR OUTPUT

A narrowband 2nd IF MON(itor) output is available from both receivers in the assembly on rear panel receptacles. This signal is centered at 455 kHz with a bandwidth determined by the selected bandwidth. The signal level at this output is established by the AGC circuits to be approximately -3 to +3 dBm into a 50 ohm load over an input signal level range of -110 dBm (1 microvolt) to -10 dBm. As previously, the connector on the left (J7) is connected to the receiver on the left and vice versa for J8. The R-3080 has only one such connector.

On special order, an IF output converter board may be mounted inside the rear panel of the receiver. This board converts the normal 455 kHz IF signal to another frequency as determined by the requirements of the purchase order.

#### 3.8 AUDIO AND ANALOG CONNECTOR

One or two of three different types of audio connectors may be found on the rear panel of the receiver. These include a 12 contact MS connector with removable crimp contacts including both twisted pair and coaxial contacts, a 19 contact MS connector with captive solder type contacts, and a single or dual 15 pin D connector with associated barrier type terminal strips.

#### 12 CONTACT MS. REMOVABLE CRIMP

Each two-receiver assembly has a common audio and analog connector for the two receivers. This connector (J2) is a military standard type with crimp type male contacts. The cable end has socket type contacts. The connections to this connector are as follows:

| MS CONNECTOR | SIGNAL OR CONTROL         | REMARKS                  |

|--------------|---------------------------|--------------------------|

|              |                           |                          |

| A            | RECEIVER 1 AUDIO          | 600 Ohm Balanced Pair    |

| A            | RECEIVER 1 AUDIO RETURN   | 0 dBm nominal level      |

| 8            | RECEIVER 2 AUDIO          | 600 Ohm Balanced Pair    |

| 8            | RECEIVER 2 AUDIO RETURN   | 0 dBm nominal level      |

| С            | SPARE                     |                          |

| D            | SPARE                     |                          |

| Ε            | RECEIVER 1 FM VIDEO       | 1 V/KHz coax, DC coupled |

| Ε            | RECEIVER 1 FM SHIELD      | ,                        |

| F            | RECEIVER 2 FM VIDEO       | 1 V/KHz coax, DC coupled |

| F            | RECEIVER 2 FM SHIELD      | ,                        |

| G            | RECEIVER 1 SIG STR ANALOG | 0 to + 5V                |

| H            | RECEIVER 1 ANALOG COMMON  | Ground                   |

| J            | RECEIVER 2 SIG STR ANALOG | 0 to + 5V                |

| K            | RECEIVER 2 ANALOG COMMON  | Ground                   |

| L            | SHIELD                    | Chassis ground           |

| М            | SPARE                     | <b>J</b> 3               |

NOTE: Each balanced audio pair is connected to a single pin in the MS connector. Likewise, each FM video coaxial cable is connected to a single pin in the MS connector. In each case, both contacts are made by a single mating pin.

# © CUBIC COMMUNICATIONS

#### 19 CONTACT MS, CAPTIVE SOLDER

Each two-receiver assembly has a common audio and analog connector for the two receivers. The R-3080 has connections for receiver 1 only. This connector is a military standard type with solder type female contacts. The cable end has pin type contacts. The connections to this connector are as follows:

| MS CONNECTOR | SIGNAL OR CONTROL         | REMARKS                  |

|--------------|---------------------------|--------------------------|

| М            | RECEIVER 1 AUDIO          | 600 Ohm Balanced Pair    |

| N            | RECEIVER 1 AUDIO RETURN   | 0 dBm nominal level      |

| P            | RECEIVER 2 AUDIO          | 600 Ohm Balanced Pair    |

| R            | RECEIVER 2 AUDIO RETURN   | O dBm nominal level      |

| G            | RECEIVER 1 FM VIDEO       | 1 V/KHz coax, DC coupled |

| Н            | RECEIVER 1 FM SHIELD      |                          |

| K            | RECEIVER 2 FM VIDEO       | 1 V/KHz coax, DC coupled |

| L            | RECEIVER 2 FM SHIELD      |                          |

| S            | RECEIVER 1 SIG STR ANALOG | 0 to + 5V                |

| T            | RECEIVER 1 ANALOG COMMON  | Ground                   |

| U            | RECEIVER 2 SIG STR ANALOG | 0 to + 5V                |

| ٧            | RECEIVER 2 ANALOG COMMON  | Ground                   |

| Α            | SHIELD                    | Chassis ground           |

| C,D,E,F,G    | SPARES                    | -                        |

#### 15 CONTACT D, TERMINAL STRIP

Each receiver has a separate audio and analog connector plus a barrier type terminal strip. The barrier strip connection data is screened on the chassis. The connections to the 15 pin D connector are as follows:

| D  | CONNECTOR | SIGNAL OR       | CONTROL        | REMARKS                  |

|----|-----------|-----------------|----------------|--------------------------|

| 9  |           | RECEIVER        | AUDIO          | 600 Ohm Balanced Pair    |

| 10 |           | RECE I VER      | AUDIO RETURN   | 0 dBm nominal level      |

| 13 |           | <b>RECEIVER</b> | FM VIDEO       | 1 V/KHz coax, DC coupled |

| 4  |           | <b>RECEIVER</b> | FM SHIELD      |                          |

| 12 |           | RECEIVER        | SIG STR ANALOG | 0 to + 5V                |

| 11 |           | RECE I VER      | ANALOG COMMON  | Ground                   |

| 1  |           | SHIELD          |                | Chassis ground           |

| 15 |           | SPEAKER         |                |                          |

| 8  |           | SPEAKER RE      | TURN           |                          |

The barrier strip has only the speaker, speaker return, audio, audio return, and chassis ground connections. The speaker connections are labeled as follows:

| SPKR H  | Speaker high side, same as Speaker                               |

|---------|------------------------------------------------------------------|

| SPKR L  | Speaker low side, same as Speaker Return                         |

| AUDIO A | One side of audio balanced line, same as Receiver Audio          |

| AUDIO B | Other side of audio balanced line, same as Receiver Audio Return |

| GROUND  | Chassis ground, use for shield if required                       |

It is recommended that the Speaker and Speaker Return (SPKR H and SPKR L) connections not be made common with any other signal including ground.

# **<b>€** CUBIC COMMUNICATIONS

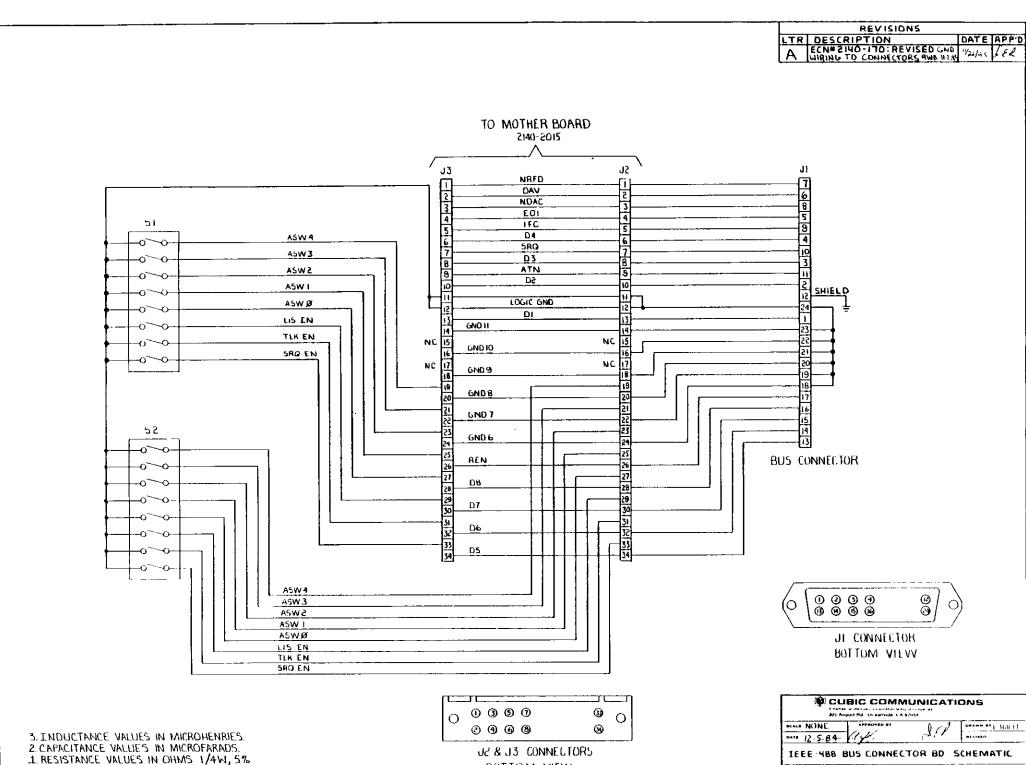

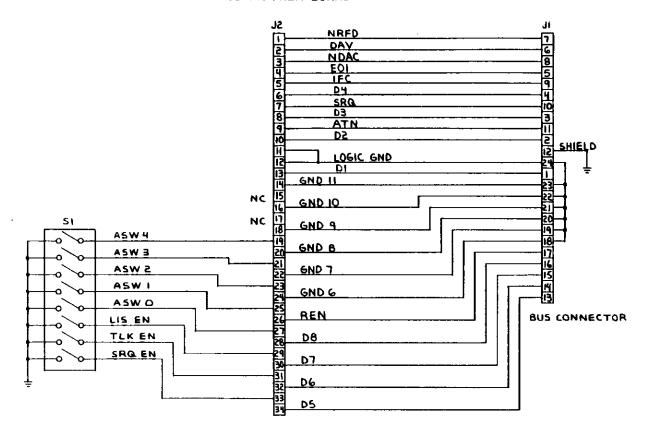

#### 3.9 IEEE-488 BUS CONNECTOR

If the unit is configured for remote control via a IEEE-488 bus, connection of the unit to the bus is made via a standard IEEE-488 bus connector, which is a 24 pin ribbon type connector. It is recommended that a commercially manufactured cable be used for this connection, being sure that both the cable and connectors are completely shielded. The receiver bus connector will be found on the conector plate on the rear panel of the receiver.

Cable requirements for the IEEE-488 bus are determined by the actual system design and reference should be made to the hardware installation instructions provided with the Bus Controller. As a general guide, however, the bus cables may be connected in either a "star" or "daisy chain" fashion, or any combination of the two, and the total cable length must not exceed 20 meters (65.5 feet) or 2 meters (6.5 feet) for each bus device connected, whichever is less. The IEEE-488 bus connector on the rear panel of the receiver is of the type specified in the IEEE-488-1972 standard and uses metric studs. Be sure the locking devices are engaged on all connectors in the system.

# 3.10 IEEE-488 ADDRESSING AND SRQ FUNCTIONS

Each individual receiver's bus address is selectable from 0 through 30 at the rear panel address switches using 5 of the 8 switches provided. The other 3 switches are used to enable the Talker Only, Listener Only, and SRQ Enable functions. In normal operation, the talker only and listener only functions are not enabled and the receiver functions both as a talker and a listener. The SRQ Enable function may be used if desired by the system controller software.

Each separate receiver in the assembly has its own set of address and function switches. These switches will be found on the connector plate on the rear panel of the assembly.

Each receiver must be configured to a unique bus address so that the controller can send information to it independently of other devices on the bus. This is done by setting the address switches on the rear panel to the desired address between 0 and 30. The address switch has eight small switches that can be in either the up (on) position or the down (off) position. The address is set into the five left most switches in a binary code with switch number A4 as the most significant bit and switch number A0 as the least significant bit. Use the following table to determine the binary code required:

TABLE 4-1

ADDRESS SWITCHES

| BUS     | CODE  | BUS     | CODE  | BU\$    | CODE  |

|---------|-------|---------|-------|---------|-------|

| ADDRESS | 43210 | ADDRESS | 43210 | ADDRESS | 43210 |

|         |       |         |       |         |       |

| 0       | 00000 | 10      | 01010 | 20      | 10100 |

| 1       | 00001 | 11      | 01011 | 21      | 10101 |

| 2       | 00010 | 12      | 01100 | 22      | 10110 |

| 3       | 00011 | 13      | 01101 | 23      | 10111 |

| 4       | 00100 | 14      | 01110 | 24      | 11000 |

| 5       | 00101 | 15      | 01111 | 25      | 11001 |

| 6       | 00110 | 16      | 10000 | 26      | 11010 |

| 7       | 00111 | 17      | 10001 | 27      | 11011 |

| 8       | 01000 | 18      | 10010 | 28      | 11100 |

| 9       | 01001 | 19      | 10011 | 29      | 11101 |

|         |       |         |       | 30      | 11110 |

NOTE: 0 = SWITCH DOWN, 1 = SWITCH UP

For all normal applications, set the T and L switches to the down position and the S switch to the up position.

If the switches are changed while the power is applied, the POWER switch must momentarily turned off and then back on for the unit to recognize the new address. When choosing addresses, be sure that the number selected is not in use by any other device on the bus.

#### 3.11 SERIAL BUS CONNECTOR

If the receiver is configured for serial bus control via either an RS-232 or RS-422 connection, connections must be made through the normal connector for the selected interface. The RS-232 interface uses a 25 pin D connector while the RS-422 interface uses a 37 pin D connector. The interfaces are configured at Data Terminal Equipment (DTE) with male pins on the chassis connector.

If connected directly to a computer interface also configured as DTE, a reversal of transmit and receive date and request to send and clear to send lines may be necessary. The Request to Send and Clear to Send lines may be jumpered together on the mating connector if required by the system. These reversals or jumpers will not normally be required if the units are connected through a modem.

The connections for these interfaces are listed below.

RS-232

| Signal  | Pin | Function                                            |

|---------|-----|-----------------------------------------------------|

| CHASSIS | 1   | Safety or shield ground                             |

| TXD     | 2   | Transmit Data, Status data from receiver            |

| RXD     | 3   | Receive Data, Control data to receiver              |

| RTS     | 4   | Request To Send (set true from receiver)            |

| CTS     | 5   | Clear To Send (to receiver, must be set true)       |

| DSR     | 6   | Data Set Ready (to receiver, not used)              |

| GROUND  | 7   | Logic Ground                                        |

| RLSD    | 8   | Received Line Signal Detect (to receiver, not used) |

| DTR     | 20  | Data Terminal Ready (set true from receiver)        |

RS-422

Signal Pin

| CHASS1S | 1  | Safety or shield ground                               |

|---------|----|-------------------------------------------------------|

| SD A    | 4  | Send Data, Status data from receiver                  |

| SD B    | 22 | Send Data, Status data from receiver                  |

| RD A'   | 6  | Receive Data, Control data to receiver                |

| RD B1   | 24 | Receive Data, Control data to receiver                |

| RS A    | 7  | Request to Send (set true from receiver)              |

| RS B    | 25 | Request to Send (set true from receiver)              |

| CS A'   | 9  | Clear to Send (to receiver, must be set true)         |

| CS B'   | 27 | Clear to Send (to receiver, must be set true)         |

| DM A'   | 11 | Data Mode (to receiver, not used) (Same as DSR)       |

| DM B'   | 29 | Data Mode (to receiver, not used) (Same as DSR)       |

| RR A'   | 13 | Receiver Ready (to receiver, not used) (Same as RLSD) |

| RR B'   | 31 | Receiver Ready (to receiver, not used) (Same as RLSD) |

| TR A    | 12 | Terminal Ready (set true from receiver) (Same as DTR) |

| TR B    | 30 | Terminal Ready (set true from receiver) (Same as DTR) |

#### 3.12 SERIAL BUS ADDRESSING AND CONFIGURATION

In order to operate the receiver under control of a serial data bus, certain functions must be set into the receiver and a bus address must be set. All of these functions are set using the front panel keypad and display with the functions retained even under power off conditions. In order to set the address and other configuration functions, switch the receiver power on, set the REMOTE/LOCAL switch to the LOCAL position, and follow the Special Function procedures. This procedure must be followed when initially installing the receiver in a serial bus control configuration.

The Special Functions including serial bus control are accessed by the key sequence "RCL SKIP" (or "RCL ·"). At this point, the channel display will show "Fn" indicating that the keypad is ready to take a function selection. The "KPAD" annunciator will be illuminated. At this point the operator may cancel by pressing the CAN key or select a function by pressing any number key from 1 through 0. Currently only the first 5 functions are implemented. Additionally, instead of pressing a number key, the operator may elect to clear all 100 memory channels to the default conditions by pressing the following key sequence "SKIP, 9, 1, 1, ENT". This process may be aborted at any stage before the ENT key is pressed by pressing CAN.

The 5 available functions are:

- 1 Software Version Number (Version 3.0 and up only)

- 2 Skip Memory Clear

- 3 Address Selection

- 4 Baud Rate Selection

- 5 Line Parameter Selection

Press the sequence "RCL SKIP" followed by the number of the desired special function and then follow the directions corresponding to the function pressed from the following paragraphs.

#### #1. Software Version Number

The Channel display will show "Sn" and the Frequency display will show the CPU software version number. This will be one or two digits, a point, and one or two more digits. Operator may press CAN or ENT which will return the front panel to normal operation. This function is useful mainly in maintenance.

#### #2. Skip Memory Clear

This function is used to clear the memory used to store frequencies to be skipped in sweep operation. The channel display will show "SP" and the SKIP annunciator will illuminate. The frequency display will remain blank. The operator may press CAN to cancel the operation or ENT to proceed with clearing the skip memory. In both cases the front panel will return to normal operation.

#### #3. Serial Bus Address Selection

This function allows user verification or modification of the Serial Interface address for the unit. The channel display will show "Ad" and the frequency display will show the current address as two decimal digits. If ENT or CAN is pressed the current address is unchanged and the panel reverts to normal operation. Alternatively, a new address may be entered by pressing two number keys. The first key press will cause the new digit to replace the left digit of the old address and a "-" to replace the right digit. The second key press will fill the right digit. At this time, pressing the ENT key will cause the old address to be replaced with the new address. Pressing the CAN key will cause the any new key entries to be ignored and the address will continue to be the old address. In both cases the front panel will revert to normal operation. If a new address is selected, it becomes effective immediately and is remembered when the power is turned off.

#### #4 Serial Bus Baud Rate Selection

This function allows selection of the Serial Interface baud rate from a list of options. The channel display will show "bd" and the frequency display will show the current baud rate. If ENT or CAN is pressed the current baud rate remains unchanged and the panel reverts to normal operation. If the operator presses the STEP key the frequency display will display the next selection from the list of options. Repeated pressing of the STEP key will show all options and repeat the list. At any time before pressing ENT, the operator may press CAN to retain the old baud rate and return the front panel to normal operation. Pressing ENT will cause the currently displayed baud rate to replace the old baud rate and be saved in memory. If a new baud rate is selected, it becomes effective immediately and is remembered when the power is turned off. (Available options are 110, 150, 200, 300, 600, 1200, 2400, 4800, 9600, and 19200 baud.)

# <u>Serial</u> Bus Line Parameter Selection

This function allows selection of the number of data bits, the number of stop bits and whether a parity bit is generated and if so whether parity is even or odd. The channel display will show "LP" and the frequency display will show three groups of information. From left to right these are the number of data bits ("7b" or "8b" for 7 or 8 data bits respectively), the number of stop bits ("1S" or "2S" for 1 or 2 stop bits respectively), and parity selection ("E" for even parity, "O" for odd parity, or "-" for no parity generated or checked). If ENT or CAN is pressed, the current line parameters remain unchanged and the front panel reverts to normal operation. If the operator instead presses the STEP key, the frequency display will cycle through the list of options. All 12 combinations of the three parameters are available and will appear in the display before the list repeats. At any time before pressing ENT, the operator may press CAN to retain the old line parameter selection. Pressing ENT will cause the currently displayed combination of line parameters to replace the old parameters and be saved in memory. If new line parameters are selected, they become effective immediately and are remembered when the power is turned off.

# 4.0 OPERATION

The receiver can be operated either by an operator using the front panel controls or remotely using a computer or bus controller. The receiver may be supplied with a remote control interface for an IEEE-488 bus, or a serial remote control interface for the bus ordered.

When operating the receiver, it is ordinarily desirable to set the receiver parameters in the following manner for signals having the indicated characteristic.

| Signal    | Bandwidth    | Mode       | AGC  | BFO or 1F Shift          | Remarks               |

|-----------|--------------|------------|------|--------------------------|-----------------------|

| AM Voice  | 4 to 8 kHz   | AM         | N/A  | N/A                      | Average AGC           |

| SSB Voice |              | LSB or USB | . 25 |                          | Automatic from panel  |

| SSB Voice | 2 to 4 kHz   | CW         | 3.0  | $1F \pm 2.3 \text{ kHz}$ | Wideband Voice        |

| CW Morse  | .3 to .5 kHz | CW         | .25  | BFO .8 TO 1kHz           | Operator Preference   |

| SSB Data  | .3 to 1 kHz  | CW         | .05  | BFO 1 to 3 kHz           | Narrow Band data      |

| SSB Data  | 1 to 4 kHz   | CW         | .05  | BFO 1 to 3 kHz           | Wide Band data        |

| FSK Data  | .5 to 1 kHz  | Frequency  | .05  | N/A                      | Narrow Band date      |

| FSK Data  | 1 to 4 kHz   | Frequency  | .05  | N/A                      | Wide Band data        |

| Pulse     | 8 kHz        | AM         | Off  | N/A                      | Manual gain reduction |

| Sweep     | 8 kHz        | CW         | .05  | BFO 1 kHz                | Search for Unknown    |

The LSB and USB modes select one bandwidth and IF shift automatically with no operator intervention necessary or possible. The bandwidth and shift are chosen to be optimum or as specified by the purchase order.

It is important to note that the receiver frequency set for all but LSB or USB modes is the center of the information band and does not bear any particular relationship to the carrier frequency for SSB voice or data signals while receiving in the CW mode. The IF shift function may be used to shift the apparent bandwidth with respect to the indicated frequency in the CW mode or the BFO offset may be used to vary the apparent pitch of the signal centered on the indicated frequency. Using IF shift, the apparent pitch remains the same while the position of the bandwidth varies with respect to the carrier frequency.

In all cases using the CW mode, the BFO signal is used to substitute for the carrier signal and the true carrier frequency will be equal to the indicated receiver frequency plus the BFO offset with a zero beat condition. The BFO offsets will be negative for USB signals and positive for LSB signals.

The frequency detector can be used to demodulate or determine the frequency shift of FSK data signals. A more optimum detection process will be to use the product detector in CW mode and process the resultant tones through a suitable audio modem. This technique will take advantage of narrower bandwidth filters in the audio modem and can result in data copy even in cases where selective fading has temporarily removed one of the tones.

#### 4.1 MANUAL OPERATION

Manual operation is performed using the 20 button keypad, front panel displays, and adjustment knob. The front panel volume control is used to vary the signal level to the headphone jacks only and does not affect the level of signal supplied to the 600 0hm balanced line. To select manual operation, set the front panel LOCAL/REMOTE switch to the LOCAL position and turn the power switch on. The receiver will power up with the frequency and other parameters last set into it before power was removed.

In order to adjust the receiver parameters, locate the parameter desired to be changed or reviewed below. Follow the instructions and indications listed and refer to the control panel pictorial in Figure 4-1.

# 4.1.1 Normal State -- Press CAN or ENT for the normal state

In the normal state (that is, no attempt is being made to change any of the numeric parameters), the display indicates the following information:

- Function -- If the frequency and other parameters have been recalled from memory, this display indicates the 2 digit memory indication, otherwise the display is dark.

- Frequency -- Display indicates the frequency in MHz -- carrier frequency in LSB or USB, center frequency in the other modes. The digit selected for tuning will be of higher intensity.

- Mode -- A single letter -- L for LSB, U for USB, C for CW, A for AM, F for FM.

- Bandwidth -- 2 numeric digits and a decimal point indicating the nominal bandwidth as ordered as option items.

- AGC -- 2 numeric digits and a decimal point indicating the nominal AGC hold time -- 0.0, .05, .25, and 3.0. Display is dark if manual gain control has been selected.

- METER -- 2 annunciators, if neither one is illuminated, the bargraph meter indicates RF signal strength; if the AUDIO annunciator is illuminated, the meter indicates audio output level; if the FREQ annunciator is illuminated, the meter indicates the relative frequency of the input signal with respect to the band center -- each bar represents 5% of the bandwidth selected.

- REM -- Dark annunciator in local control

- FAULT -- Dark annunciator in the absence of a fault

- KPAD -- Dark annunciator

- SKIP -- Annunciator used in Scan operations only.

FIGURE 4-1

CONTROL PANEL PICTORIAL

# 4.1.2 Direct Function Changes

MODE -- Press the MODE (7) key from the normal state

Observe the MODE letter change, select the mode desired

C is CW, A is AM, L is LSB, U is USB, and F is FM

BANDWIDTH -- Press the BW (8) key from the normal state

Observe the BW value change, select the bandwidth desired

Note that bandwidth is always fixed in LSB or USB

AGC -- Press the AGC (9) key from the normal state

Observe the AGC hold time value change from off (dark), 0.0,

.05, .25, and 3.0 seconds

METER -- Press the METR key

Observe the meter annunciators change from dark to AUDIO to FREQ to dark again and observe the bargraph meter indication change accordingly.

When the annunciator is dark, the meter indicates input signal strength (when AGC is enabled) from -120 to 0 dBm (into 50 0hms). Each segment of the display represents approximately 6 dB. When AGC is disabled, the manual gain control can be used to position the indication to the middle of the meter scale.

When the annunciator indicates AUD10, the meter indicates audio output level to the 600 Ohm line from -30 to +4 dBm (with a 600 Ohm load). Each segment of the display represents approximately 2 dB.

When the annunciator indicates FREQ, the meter indicates the approximate frequency of the signal with respect to the center of the IF bandwidth. Each segment of the display represents approximately 5% of the total IF bandwidth. Note: when exactly on the center frequency, both segments on either side of 0 should be observed to be flashing.